Page 54 Epson Research and Development

Vancouver Design Center

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

1. Ts = pixel clock period

2. t6min = [((REG[04h] bits 6-0)+1) x 8 + ((REG[08h] bits 4-0)+4) x 8] Ts

3. t8 min = [((REG[06h] bits 1-0, REG[05h] bits 7-0)+1) + (REG[0Ah] bits 6-0)] Lines

4. t10min = [((REG[04h] bits 6-0)+1) x 8] Ts

5. t14min = [((REG[04h] bits 6-0)+1) x 8] Ts

6. t15min = [(REG[07h] bits 4-0) x 8 + 16] Ts

7. t17min = [(REG[08h] bits 4-0) - (REG[07]) x 8 + 16] Ts

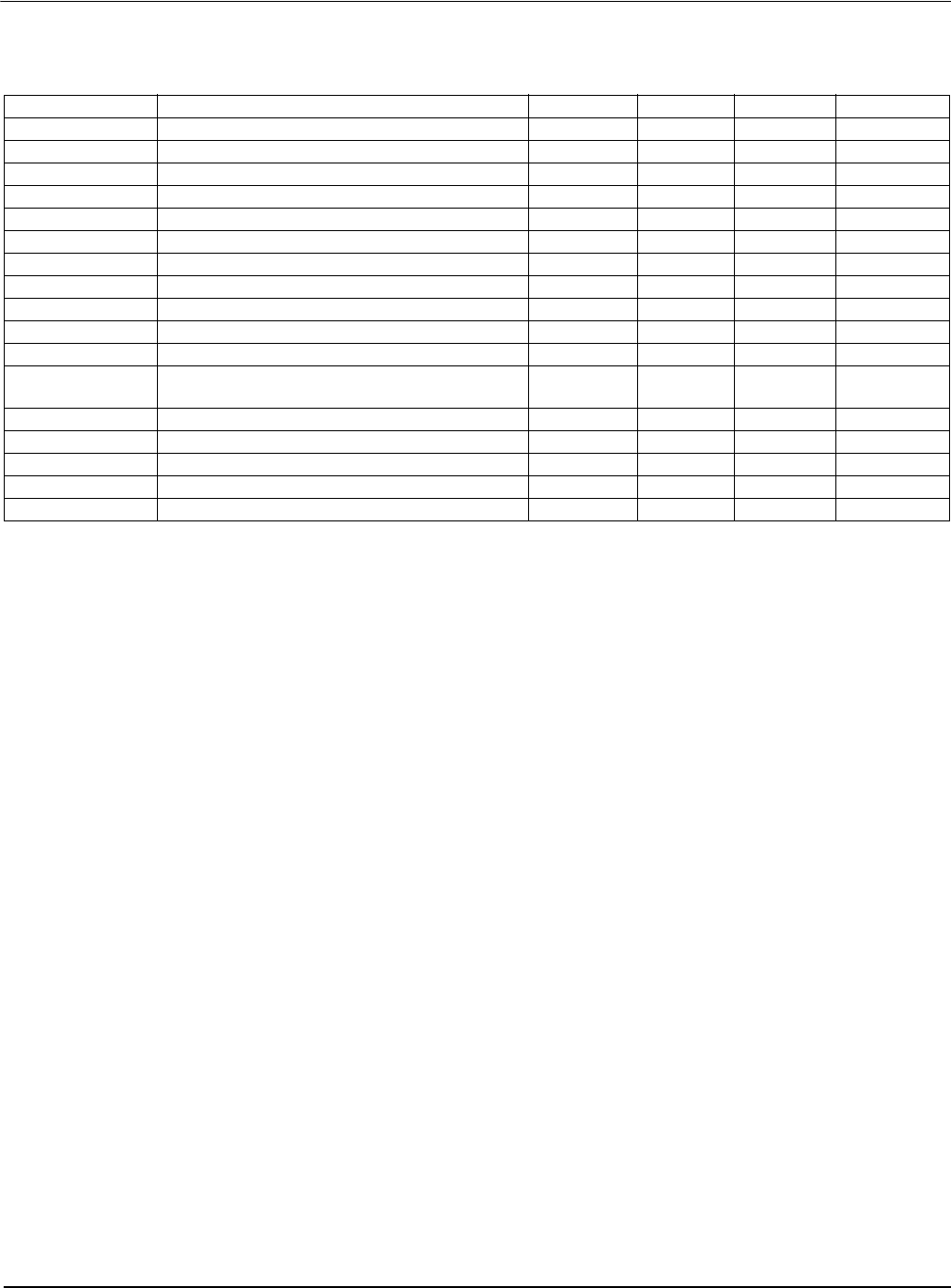

Table 7-18: TFT/D-TFD A.C. Timing

Symbol Parameter Min Typ Max Units

t1

Shift Pulse period 1 (note 1)

t2

Shift Pulse pulse width high 0.5 Ts

t3

Shift Pulse pulse width low 0.5 Ts

t4

data setup to Shift Pulse falling edge 0.5 Ts

t5

data hold from Shift Pulse falling edge 0.5 Ts

t6

Line Pulse cycle time note 2

t7

Line Pulse pulse width low 9 Ts

t8 Frame Pulse cycle time note 3

t9 Frame Pulse pulse width low 2t6

t10 horizontal display period note 4

t11 Line Pulse setup to Shift Pulse falling edge 0.5 Ts

t12

Frame Pulse falling edge to Line Pulse falling

edge phase difference

t6 - 18Ts

t13 DRDY to Shift Pulse falling edge setup time 0.5 Ts

t14 DRDY pulse width note 5

t15 DRDY falling edge to Line Pulse falling edge note 6

t16 DRDY hold from Shift Pulse falling edge 0.5 Ts

t17 Line Pulse Falling edge to DRDY active note 7 250