Epson Research and Development Page 13

Vancouver Design Center

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

.

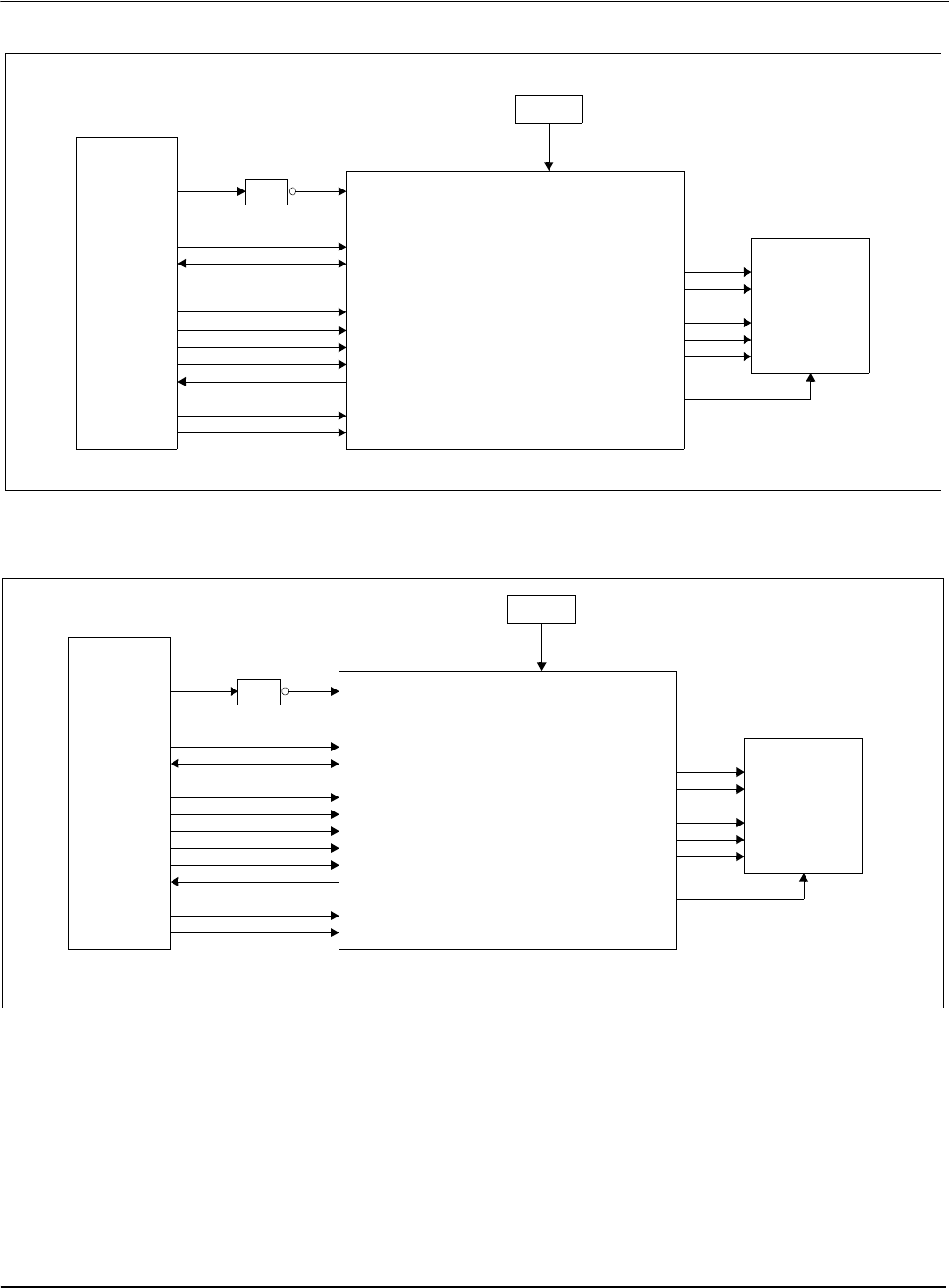

Figure 3-3: Typical System Diagram (M68K #1 Bus)

.

Figure 3-4: Typical System Diagram (M68K #2 Bus)

S1D13705

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[7:4]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

D[3:0]

4-bit

LCD

Display

MC68000

BUS

RESET#

LDS#

D[15:0]

AS#

R/W#

DTACK#

A[16:1]

CLK

AB0

RD/WR#

AB[16:1]

DB[15:0]

WE1#

BS#

CS#

BCLK

WAIT#

RESET#

A[23:17]

FC0, FC1, FC2

Decoder

UDS#

LCDPWR

S1D13705

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

D[7:0]

8-bit

LCD

Display

MC68030

BUS

RESET#

SIZ0

D[31:16]

AS#

R/W#

SIZ1

DSACK1#

A[16:0]

CLK

WE0#

RD/WR#

AB[16:0]

DB[15:0]

WE1#

BS#

RD#

CS#

BCLK

WAIT#

RESET#

A[31:17]

FC0, FC1, FC2

Decoder

DS#

LCDPWR