Page 14 Epson Research and Development

Vancouver Design Center

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

.

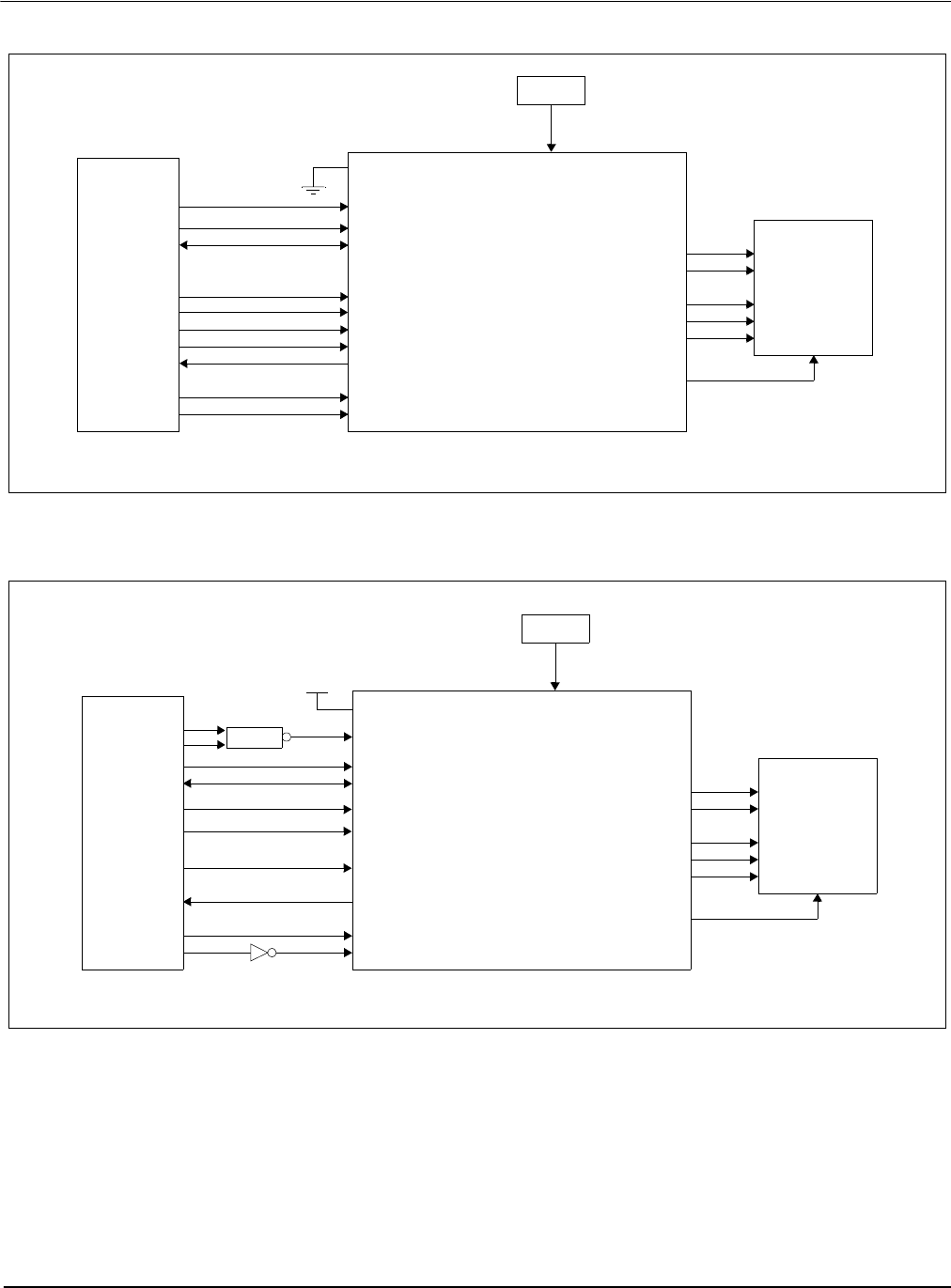

Figure 3-5: Typical System Diagram (Generic #1 Bus)

.

Figure 3-6: Typical System Diagram (Generic #2 Bus - e.g. ISA Bus)

S1D13705

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[11:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

DRDY

D[11:0]

12-bit

TFT

Display

GENERIC #1

BUS

RESET#

D[15:0]

RD0#

WAIT#

A[16:0]

BCLK

RD/WR#

AB[16:0]

DB[15:0]

WE1#

RD

CS#

BCLK

WAIT#

RESET#

CSn#

WE1#

LCDPWR

WE0#

WE0#

BS#

RD1#

S1D13705

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[8:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

DRDY

D[8:0]

9-bit

TFT

Display

ISA

BUS

RESET

SD[15:0]

SMEMR#

IOCHRDY

SA[16:0]

BCLK

AB[16:0]

DB[15:0]

WE1#

RD#

BCLK

WAIT#

RESET#

LCDPWR

WE0#

SMEMW#

BS#

Decoder

CS#

SA[19:17]

REFRESH

SBHE#