Page 58 Epson Research and Development

Vancouver Design Center

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

bit 4 Input Clock Divide

When this bit = 0, the Operating Clock(CLK) is the same as the Input Clock (CLKI).

When this bit = 1, CLK = CLKI/2.

In landscape mode PCLK=CLK and MCLK is selected as per Table 8-3: “High Perfor-

mance Selection”.

In SwivelView mode, MCLK and PCLK are derived from CLK as shown in Table 8-8:

“Selection of PCLK and MCLK in SwivelView Mode,” on page 68.

bit 3 Display Blank

This bit blanks the display image. When this bit = 1, the display is blanked (FPDAT lines

to the panel are driven low). When this bit = 0, the display is enabled.

bit 2 Frame Repeat (EL support)

This feature is used to improve Frame Rate Modulation of EL panels. When this bit = 1,

an internal frame counter runs from 0 to 3FFFFh. When the frame counter rolls over, the

modulated image pattern is repeated (every 1 hour when the frame rate is 72Hz). When

this bit = 0, the modulated image pattern is never repeated.

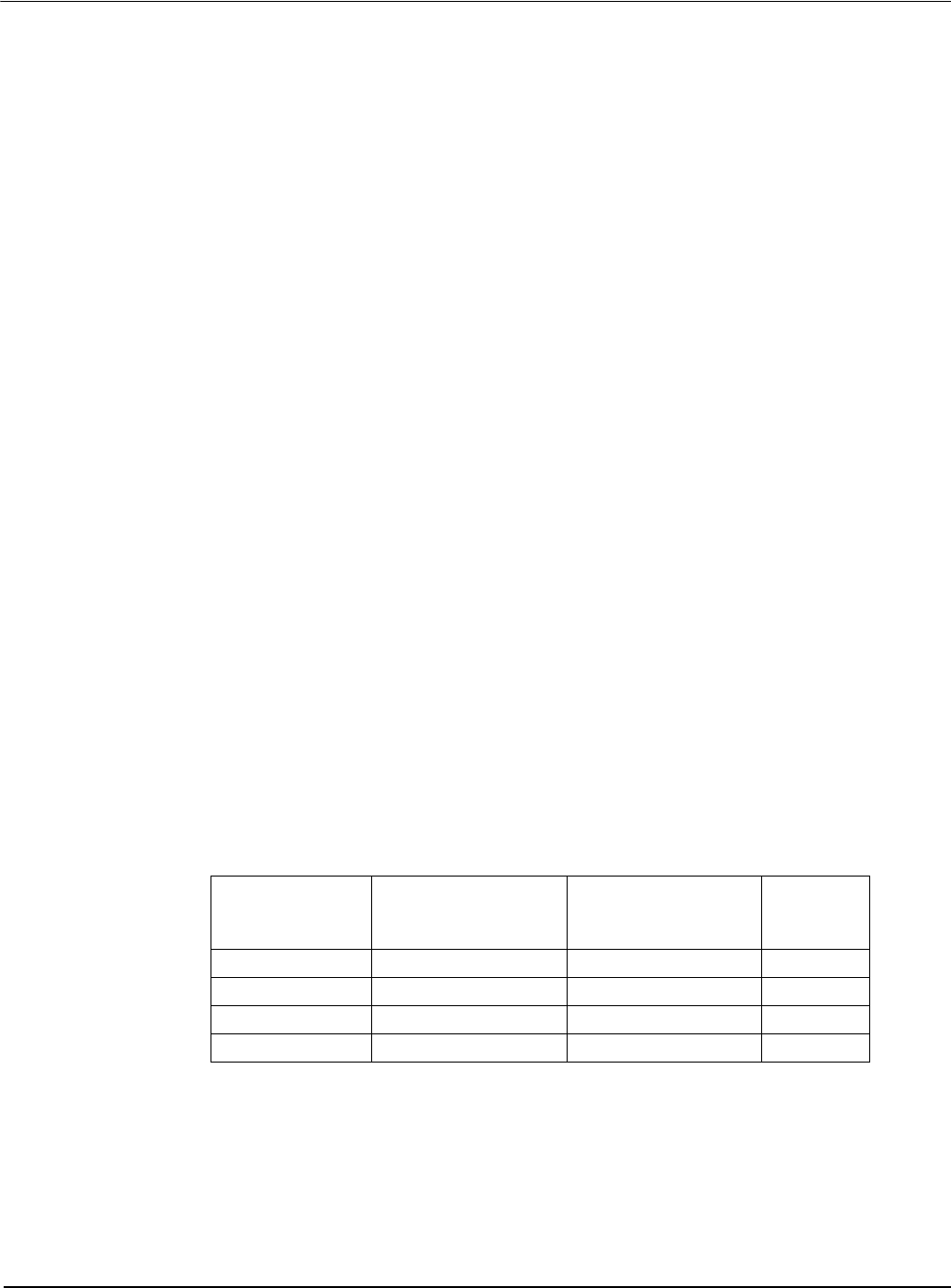

bit 1 Hardware Video Invert Enable

In passive panel modes (REG[01h] bit 7 = 0) FPDAT11 is available as either GPIO4 or

hardware video invert. When this bit = 1, Hardware Video Invert is enabled via the

FPDAT11 pin. When this bit = 0, FPDAT11 operates as GPIO4. See Table 8-4: “Inverse

Video Mode Select Options” below.

Note

Video data is inverted after the Look-Up Table.

bit 0 Software Video Invert

When this bit = 1, Inverse Video Mode is selected. When this bit = 0, Standard Video

Mode is selected. See Table 8-4: “Inverse Video Mode Select Options” below.

Note

Video data is inverted after the Look-Up Table.

Table 8-4: Inverse Video Mode Select Options

Hardware Video

Invert Enable

Software Video Invert

(Passive and Active

Panels)

FPDAT11

(Passive Panels Only)

Video Data

00 XNormal

01 XInverse

1X 0Normal

1X 1Inverse