Page 18 Epson Research and Development

Vancouver Design Center

S1D13705 Interfacing to the Motorola MPC821 Microprocessor

X27A-G-010-02 Issue Date: 01/02/13

4.3 S1D13705 Hardware Configuration

The S1D13705 uses CNF3 through CNF0 and BS# to allow selection of the bus mode and

other configuration data on the rising edge of RESET#. Refer to the S1D13705 Hardware

Functional Specification, document number X27A-A-001-xx for details.

The tables below show only those configuration settings important to the MPC821

interface. The settings are very similar to the ISA bus with the following exceptions:

• the WAIT# signal is active high rather than active low.

• the Power PC is big endian rather than little endian.

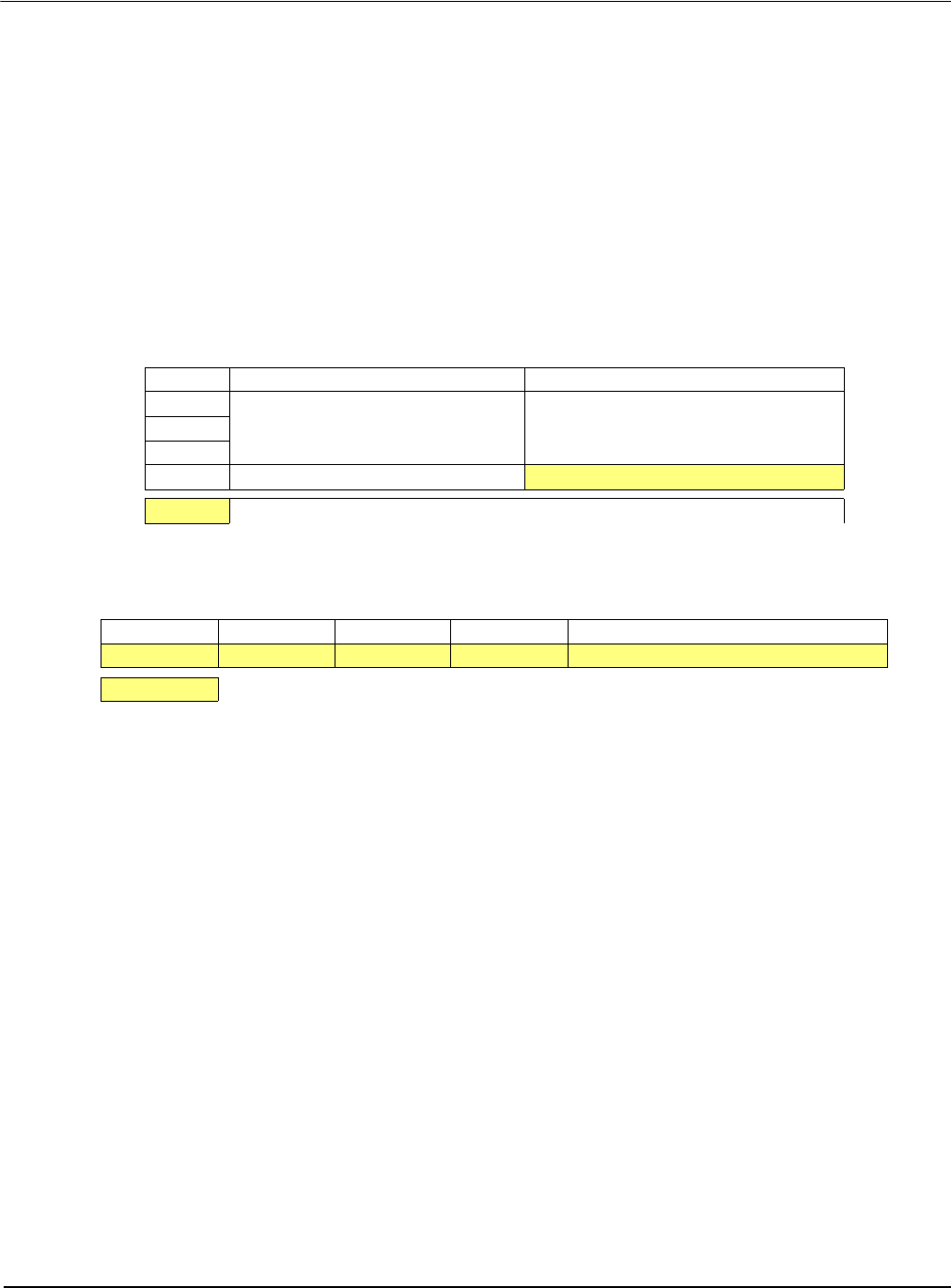

Table 4-2: Configuration Settings

Signal Low High

CNF0

See “Host Bus Selection” table below See “Host Bus Selection” table belowCNF1

CNF2

CNF3 Little Endian

Big Endian

= configuration for MPC821 host bus interface

Table 4-3: Host Bus Selection

CNF2 CNF1 CNF0 BS# Host Bus Interface

1 1 1 0 Generic #1, 16-bit

= configuration for MPC821 host bus interface