Epson Research and Development Page 45

Vancouver Design Center

Programming Notes and Examples S1D13705

Issue Date: 02/01/22 X27A-G-002-03

For this example the Horizontal Non-Display register [REG[08h]) needs to be set to 07h

and the Vertical Non-Display register (REG[0Ah]) needs to be set to 03h.

The 16,000,000/2 in the formula above represents the input clock being divided by two

when this alternate portrait mode is selected. With the values given for this example we

must ensure the Input Clock Divide bit (REG[02h] b4) is reset (with the given values it was

likely set as a result of the frame rate calculations for landscape display mode).

No other registers need to be altered.

The display is now configured for portrait mode use. Offset zero of display memory corre-

sponds to the upper left corner of the display. Display memory is accessed exactly as it was

for landscape mode.

As this is the alternate portrait mode the power of two stride issue encountered with the

default portrait mode is no longer an issue. The stride is the same as the portrait mode width.

In this case 120 bytes.

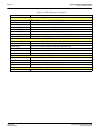

FrameRate

PCLK

HDP HNDP+()VDP VNDP+()×

-----------------------------------------------------------------------------------------=

FrameRate

16 000 000,,

2

------------------------------

320 88+()240 3+()×

------------------------------------------------------- 8 0 . 6 9==