Epson Research and Development Page 15

Vancouver Design Center

S5U13705B00C Rev. 2.0 Evaluation Board User Manual S1D13705

Issue Date: 2002/09/16 X27A-G-014-02

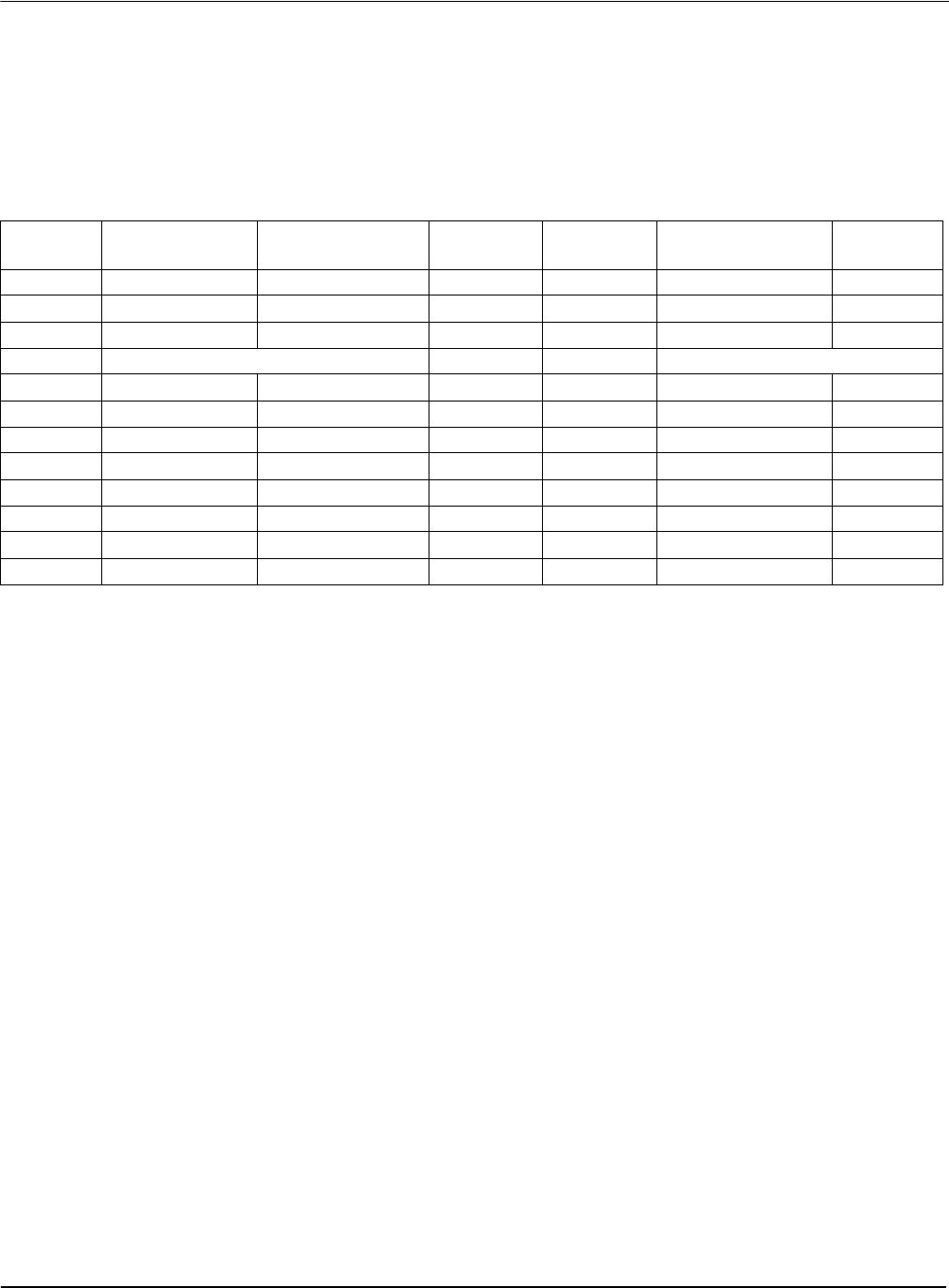

4 CPU Interface

4.1 CPU Interface Pin Mapping

Note

1

If the target MC68K bus is 32-bit, then these signals should be connected to D[31:16].

Table 4-1: CPU Interface Pin Mapping

S1D13705

Pin Name

Generic #1 Generic #2 Hitachi SH-3 Hitachi SH-4

Motorola

MC68K #1

Motorola

MC68K #2

AB[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1]

AB0 A0 A0 A0 A0 LDS# A0

DB[15:0] D[15:0] D[15:0] D[15:0] D[15:0] D[15:0] D[15:0]

1

CS# External Decode CSn# CSn# External Decode

BCLK BCLK BCLK CKIO CKIO CLK CLK

BS# Connect to VSS Connect to IOVDD BS# BS# AS# AS#

RD/WR# RD1# Connect to IOVDD RD/WR# RD/WR# R/W# R/W#

RD# RD0# RD# RD# RD# Connect to IOVDD SIZ1

WE0# WE0# WE# WE0# WE0# Connect to IOVDD SIZ0

WE1# WE1# BHE# WE1# WE1# UDS# DS#

WAIT# WAIT# WAIT# WAIT# RDY# DTACK# DSACK1#

RESET# RESET# RESET# RESET# RESET# RESET# RESET#