Epson Research and Development Page 41

Vancouver Design Center

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

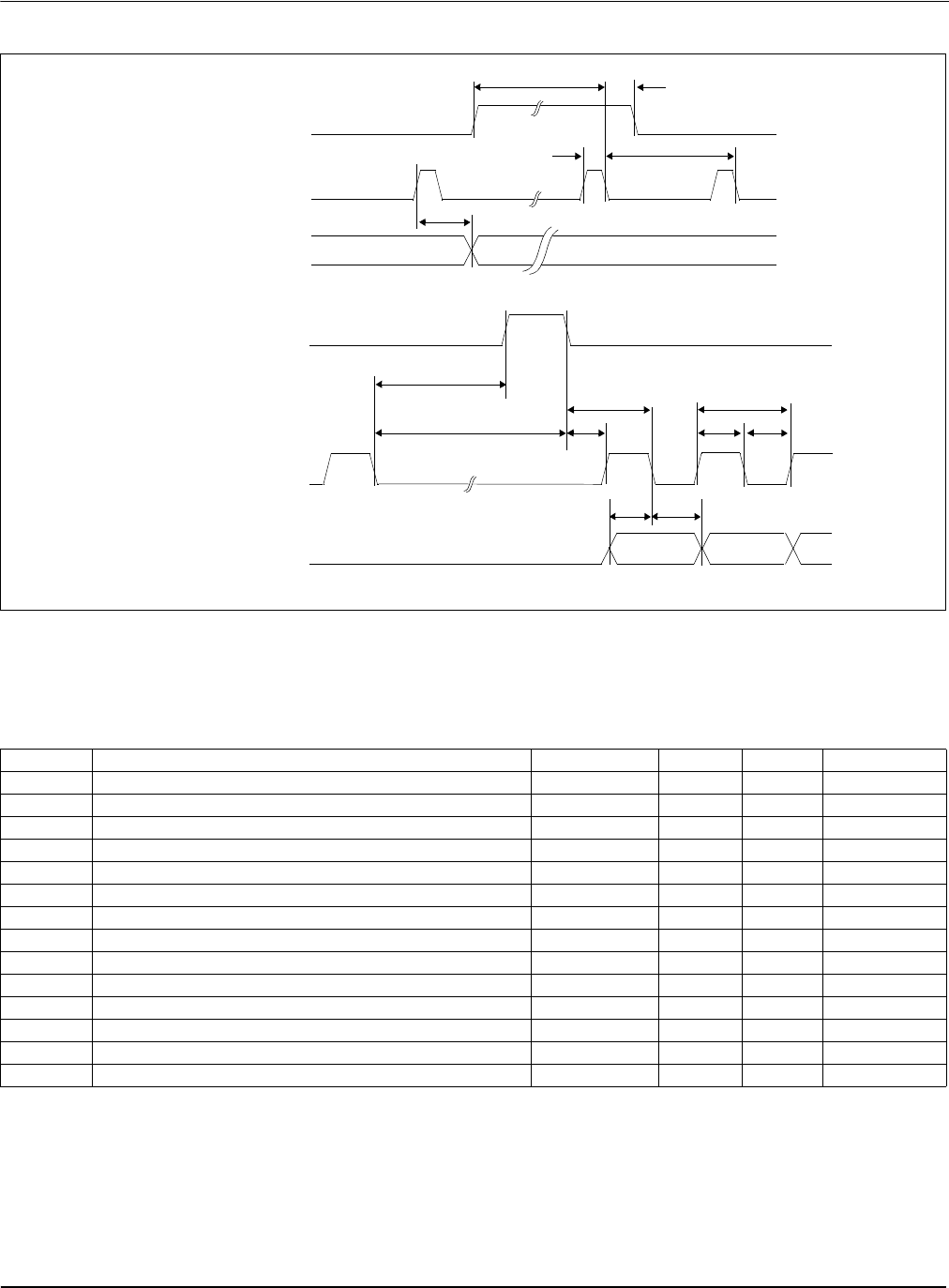

Figure 7-14: Single Monochrome 8-Bit Panel A.C. Timing

1. Ts = pixel clock period

2. t1

min

= t3

min

- 9Ts

3. t3

min

= [((REG[04h] bits 6-0)+1) x 8 + ((REG[08h] bits 4-0) + 4) x 8]Ts

4. t6

min

= [(REG[08h] bits 4-0) x 8 + 4]Ts

5. t7

min

=[(REG[08h] bits 4-0) x 8 + 13]Ts

Table 7-12: Single Monochrome 8-Bit Panel A.C. Timing

Symbol Parameter Min Typ Max Units

t1 Frame Pulse setup to Line Pulse falling edge note 2 (note 1)

t2 Frame Pulse hold from Line Pulse falling edge 9 Ts

t3 Line Pulse period note 3

t4 Line Pulse pulse width 9 Ts

t5 MOD delay from Line Pulse rising edge 1 Ts

t6 Shift Pulse falling edge to Line Pulse rising edge note 4

t7 Shift Pulse falling edge to Line Pulse falling edge note 5

t8 Line Pulse falling edge to Shift Pulse falling edge t14 + 4 Ts

t9 Shift Pulse period 8 Ts

t10 Shift Pulse pulse width low 4 Ts

t11 Shift Pulse pulse width high 4 Ts

t12 FPDAT[7:0] setup to Shift Pulse falling edge 4 Ts

t13 FPDAT[7:0] hold to Shift Pulse falling edge 4 Ts

t14 Line Pulse falling edge to Shift Pulse rising edge 23 Ts

t12 t13

Frame Pulse

Line Pulse

DRDY (MOD)

Sync Timing

Line Pulse

Shift Pulse

FPDAT[7:0]

Data Timing

t5

t1

t2

t3

t4

t14

t8 t9

t10t11

12

t7

t6

Note: For this timing diagram Mask FPSHIFT, REG[01h] bit 3, is set to 1