IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

104 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

5.6.2.3 Receiver Operational Overview

The receiver structure performs Clock and Data Recovery (CDR) on the incoming serial data

stream. The quality of this operation is a dominant factor for the Bit Error Rate (BER) system

performance. Feed forward and feedback controls are combined in one receiver architecture for

enhanced performance. The data is over-sampled and a digital circuit detects the edge position in

the data stream. A signal is not generated if an edge is not found. A feedback loop takes care of

low-frequency jitter phenomenon of unlimited amplitude, while a feed forward section suppresses

high-frequency jitter having limited amplitude. The static edge position is held at a constant

position in the over-sampled by a constant adjustment of the sampling phases with the early and

late signals.

5.6.2.4 Selective Power-Down

The IXF1104 offers the ability to selectively power-down any of the SerDes TX or RX ports that

are not being used. This is done via “TX and RX Power-Down ($0x787)” on page 219.

5.6.2.5 Receiver Jitter Tolerance

The SerDes receiver architecture is designed to track frequency mismatch, recover phase, and is

tolerant of low-frequency data jitter. Figure 23 specifies the SerDes core receiver sinusoidal jitter

tracking capabilities.

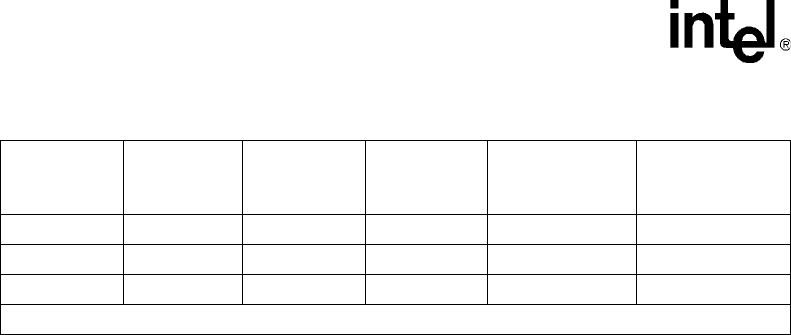

1 0 1 1 2.0 20 mA

1 1 0 1 1.0 10 mA

1110 0.5 5 mA

Table 29. SerDes Driver TX Power Levels

DRVPWRx[3] DRVPWRx[2] DRVPWRx[1] DRVPWRx[0]

Normalized

Driver Power

Setting

Driver Power

NOTE: All other values are reserved.