IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

Datasheet 89

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

5.2.2.8.1 Clock Rates

The TFCLK and RFCLK can be independent of each other in SPHY mode operation. TFCLK and

RFCLK should be common to all the Network Processor devices. The IXF1104 requires an

individual single clock source for the device transmit path and a single clock source for the device

receive path.

The IXF1104 allows this interface to be overclocked so that all four IXF1104 ports can operate at

1 Gbps. This allows data transfer at data rates of up to 4.0 Gbps when operating at an overclocked

frequency of 125 MHz.

Note: SPHY operates at a maximum frequency of 125Mhz.

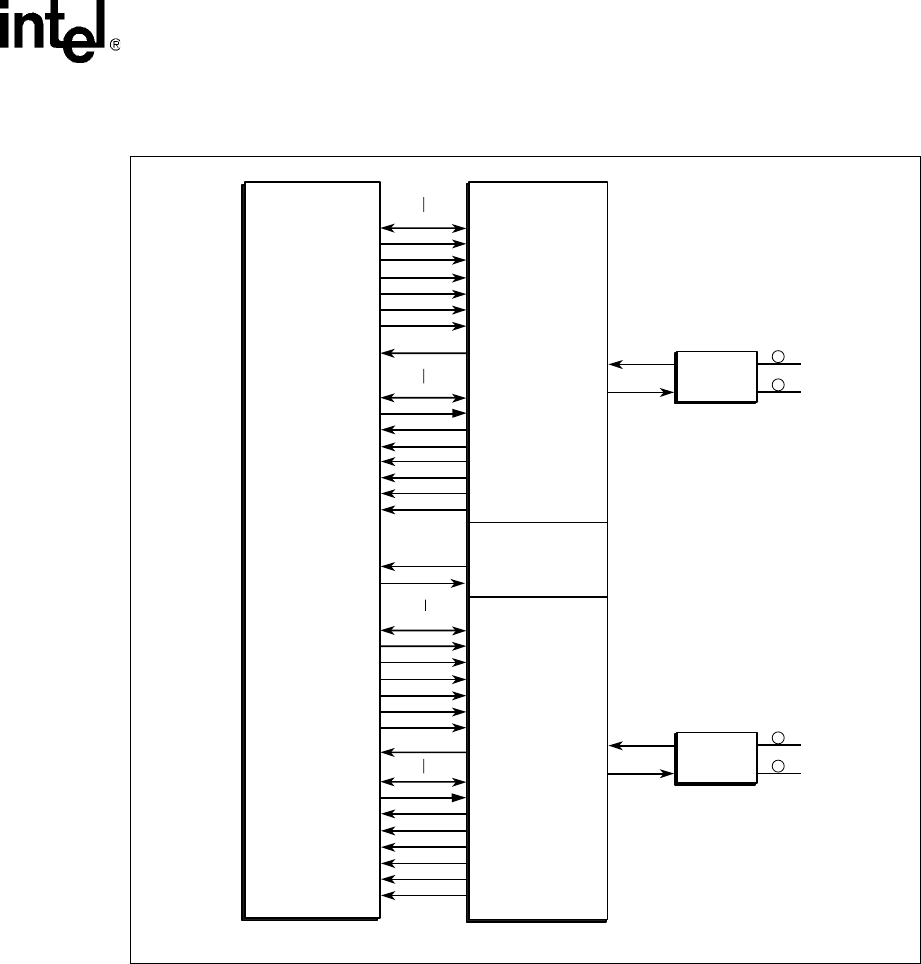

Figure 16. SPHY Connection for Two IXF1104 Ports (8-Bit Interface)

B0659-02

TFCLK

TENB[0]

TDAT[7:0][0]

TPRTY[0]

TERR[0]

TSOP[0]

TEOP[0]

Network Processor

SPI3 Bus

Intel

®

IXF1104

Port 0

TFCLK

TENB_0

TDAT[7:0]_0

TPRTY_0

TERR_0

TSOP_0

TEOP_0

RFCLK

RENB[0]

RDAT[7:0][0]

RPRTY[0]

RPRTY_0

RVAL[0]

RERR[0]

RSOP[0]

REOP[0]

RFCLK

RENB_0

RDAT[7:0]_0

RVAL_0

RERR_0

RSOP_0

REOP_0

DTPA[0]

TFCLK

TENB[1]

TDAT[7:0][1]

TPRTY[1]

TERR[1]

TSOP[1]

TEOP[1]

RFCLK

RENB[1]

RDAT[7:0][1]

RPRTY[1]

RPRTY_1

RVAL[1]

RERR[1]

RSOP[1]

REOP[1]

DTPA[1]

DTPA_0

Transceiver

Port 1

SPI3

Flow Control

TFCLK

TENB_1

TDAT[7:0]_1

TPRTY_1

TERR_1

TSOP_1

TEOP_1

RFCLK

RENB_1

RDAT[7:0]_1

RVAL_1

RERR_1

RSOP_1

REOP_1

DTPA_1

Transceiver

Port 0

Port 1

Line-Side

Interface

Line-Side

Interface

PTPA

TADR[1:0]

PTPA

TADR[1:0]