IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 181

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

12

Auto-Negotiation

Enable

0 = Disable auto-negotiation process

1 = Enable auto-negotiation process

This register bit must be enabled for

1000BASE-T operation.

RO 1

11 Power-Down

0 = Normal operation

1 = Power-down

RO 0

10 Isolate

0 =

1 = Electrically isolate PHY from GMII

RO 0

9

Restart

Auto-Negotiation

0 = Normal operation

1 = Restart auto-negotiation process

RO 0

8 Duplex Mode

0 = Half-duplex mode

1 = Full-duplex mode

RO 1

2

7 Collision Test

0 = Disable COL signal test

1 = Enable COL signal test

This register bit is ignored unless loopback is

enabled (Register bit 0.14 = 1)

RO 0

6

Speed Selection

1000 Mbps

0.6 (Speed<1>) 0.13 (Speed<0>)

00 = 10 Mbps

01 = 100 Mbps

10 = 1000 Mbps (manual mode now allowed)

11 = Reserved

RO 0

2

5:0 Reserved Reserved RO 0

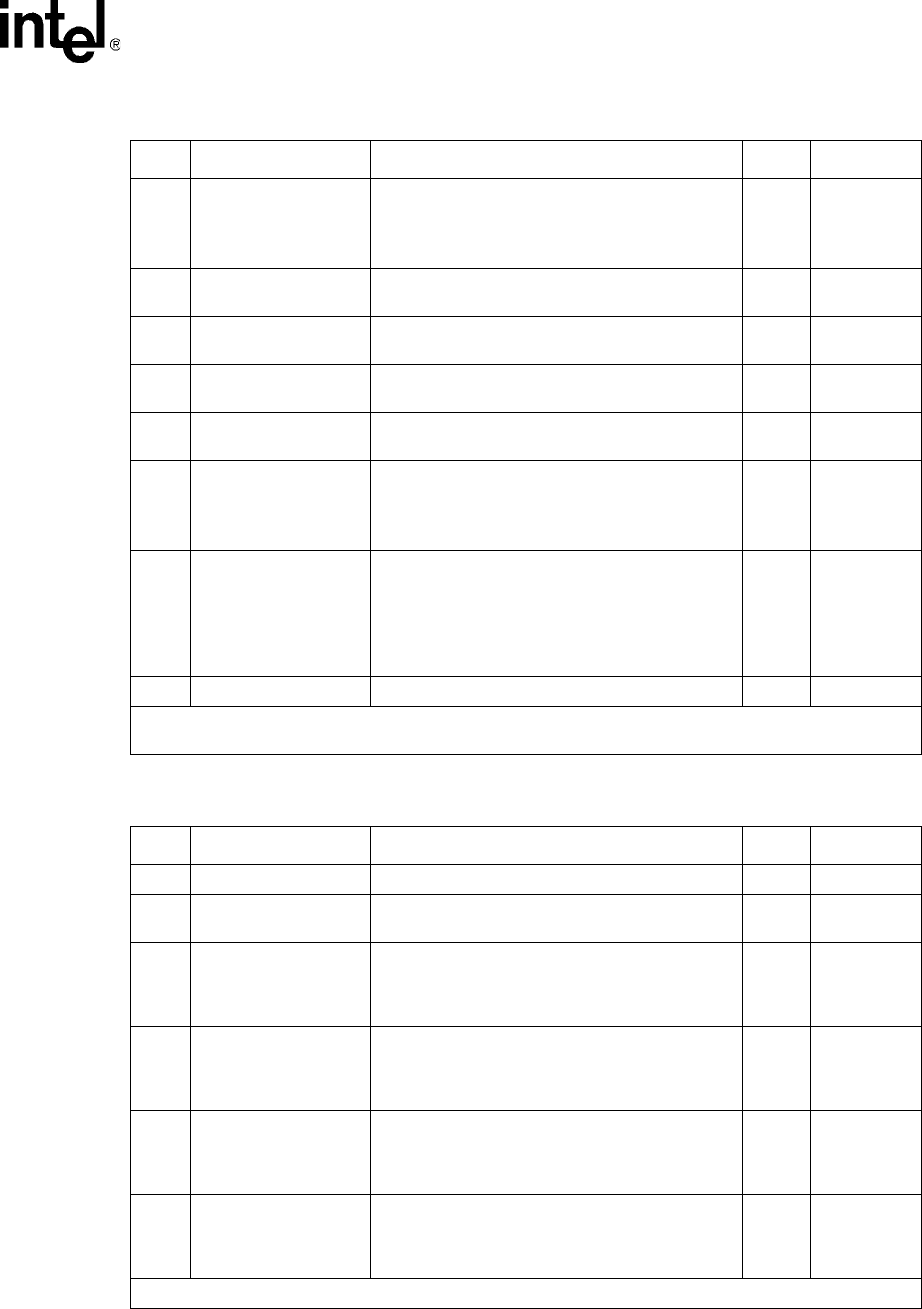

Table 96. PHY Status ($ Port Index + 0x61) (Sheet 1 of 2)

Bit Name Description Type

1

Default

31:16 Reserved Reserved RO 0

15 100BASE-T4

0 = PHY not able to operate in 100BASE-T4

1 = PHY able to operate in 100BASE-T4

RO 0

14

100BASE-X

Full-Duplex

0 = PHY not able to operate in 100BASE-X in full-

duplex mode

1 = PHY able to operate in 100BASE-X in full-

duplex mode

RO 1

13

100BASE-X

Half-Duplex

0 = PHY not able to operate in 100BASE-X in

half-duplex mode

1 = PHY able to operate in 100BASE-X in half-

duplex mode

RO 1

12

10 Mbps

Full-Duplex

0 = PHY not able to operate in 10 Mbps in full-

duplex mode

1 = PHY able to operate in 10 Mbps in full-duplex

mode

RO 1

11

10 Mbps

Half-Duplex

0 = PHY not able to operate in 10 Mbps in half-

duplex mode

1 = PHY able to operate in 10 Mbps in half-

duplex mode

RO 1

1. R = Read Only; RR = Clear on Read; W = Write; R/W = Read/Write

Table 95. PHY Control ($ Port Index + 0x60) (Sheet 2 of 2)

Bit Name Description Type

1

Default

1. RO = Read Only; RR = Clear on Read; W = Write; R/W = Read/Write

2. This register is ignored if auto-negotiation is enabled.