IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

Datasheet 121

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

5.9.1.3 CPU Timing Parameters

For information on the CPU interface Read and Write cycle AC timing parameters, refer to Figure

47 “CPU Interface Read Cycle AC Timing” on page 148, Figure 48 “CPU Interface Write Cycle

AC Timing” on page 148, and Table 54 “CPU Interface Write Cycle AC Signal Parameters” on

page 149.

5.9.2 Endian

The Endian of the CPU interface may be changed to allow connection of various CPUs to the

IXF1104 4-Port Gigabit Ethernet Media Access Controller. The Endian selection is determined by

setting the Endian bit in the “CPU Interface ($0x508)".

The following describes Endianness control:

• There is a byte swapper between the internal 32-bit bus and the external 32-bit bus.

• In 8-bit or 16-bit mode operation, the byte packer/byte unpacker holding registers sink and

source data just like the 32-bit external bus in 32-bit mode.

• The “CPU Interface ($0x508)" selects Big-Endian or Little-Endian mode.

• The byte swapper causes the behavior seen in Table 37 for accessing a register with data bits

data[31:0].

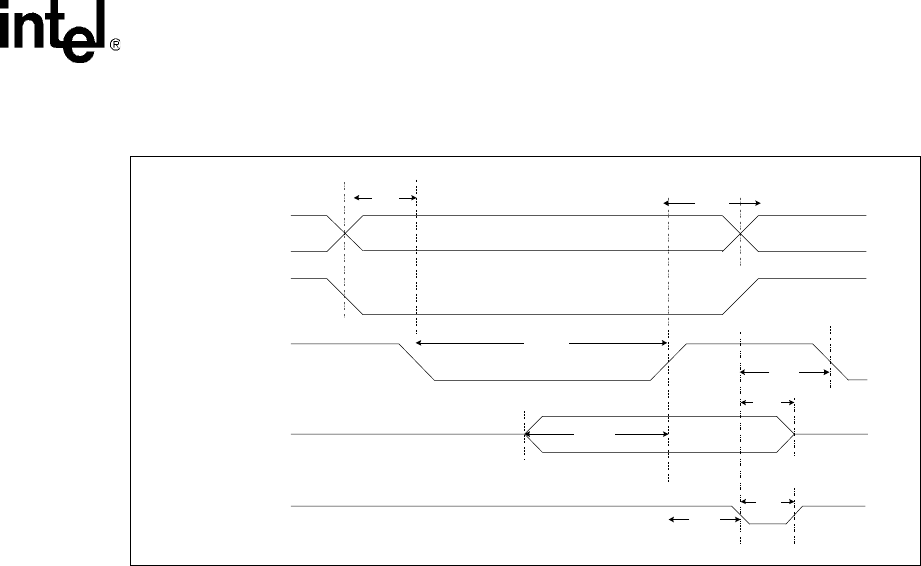

Figure 32. Write Timing Diagram - Asynchronous Interface

TCAS

TCAH

TCWL

TCDWS

TCDWD

TCYD

TCWH

uPx_Add[12:0]

uPx_WrN

uPx_CsN

uPx_Data[31:0]

uPx_RdyN

TCDWH