IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 207

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

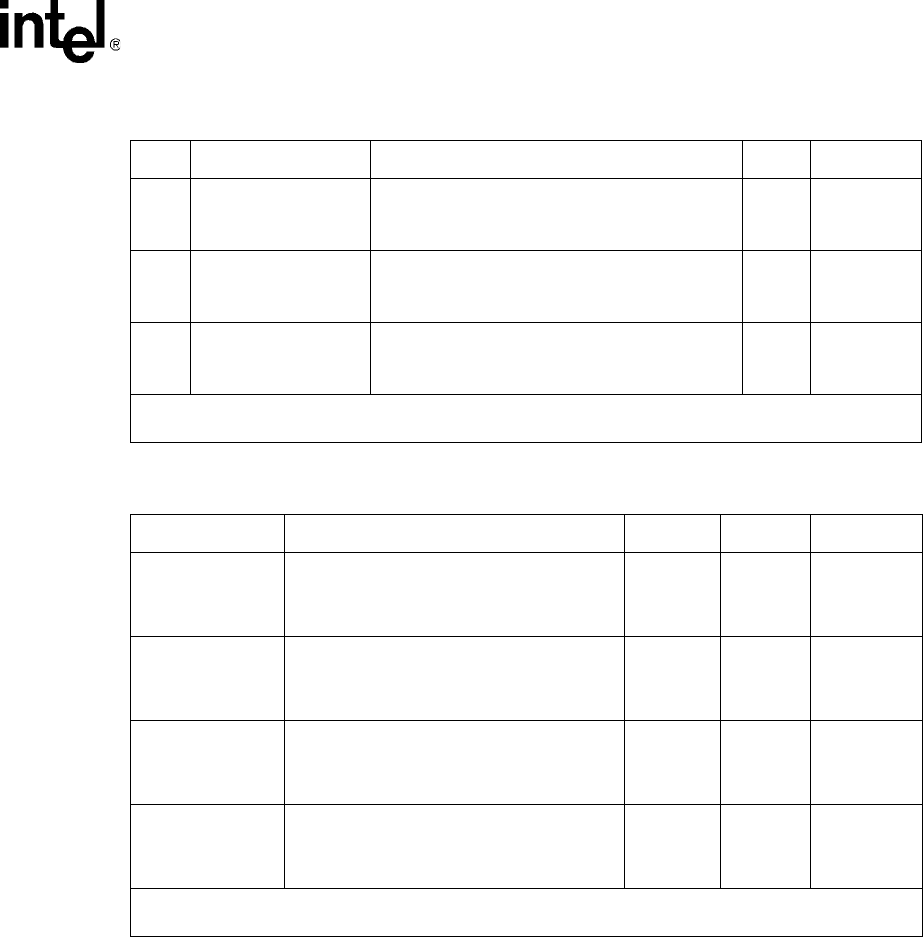

2Port 2 Reset

Port 2

0 = De-assert Reset

1 = Assert Reset

R/W 0

1Port 1 Reset

Port 1

0 = De-assert Reset

1 = Assert Reset

R/W 0

0Port 0 Reset

Port 0

0 = De-assert Reset

1 = Assert Reset

R/W 0

Table 138. TX FIFO Overflow Frame Drop Counter Ports 0 - 3 ($0x621 – 0x624)

Name Description Address Type

*

Default

TX FIFO overflow

frame drop counter

on Port 0

When TX FIFO on Port 0 becomes full or

reset, the number of frames lost or removed

on this port is shown in this register. This

register is cleared on Read.

0x621 R 0x00000000

TX FIFO overflow

frame drop counter

on Port 1

When TX FIFO on Port 1 becomes full or

reset, the number of frames lost or removed

on this port is shown in this register. This

register is cleared on Read.

0x622 R 0x00000000

TX FIFO overflow

frame drop counter

on Port 2

When TX FIFO on Port 2 becomes full or

reset, the number of frames lost or removed

on this port is shown in this register. This

register is cleared on Read.

0x623 R 0x00000000

TX FIFO overflow

frame drop counter

on Port 3

When TX FIFO on Port 3 becomes full or

reset, the number of frames lost or removed

on this port is shown in this register. This

register is cleared on Read.

0x624 R 0x00000000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 137. TX FIFO Port Reset ($0x620) (Sheet 2 of 2)

Bit Name Description Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write