IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 205

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

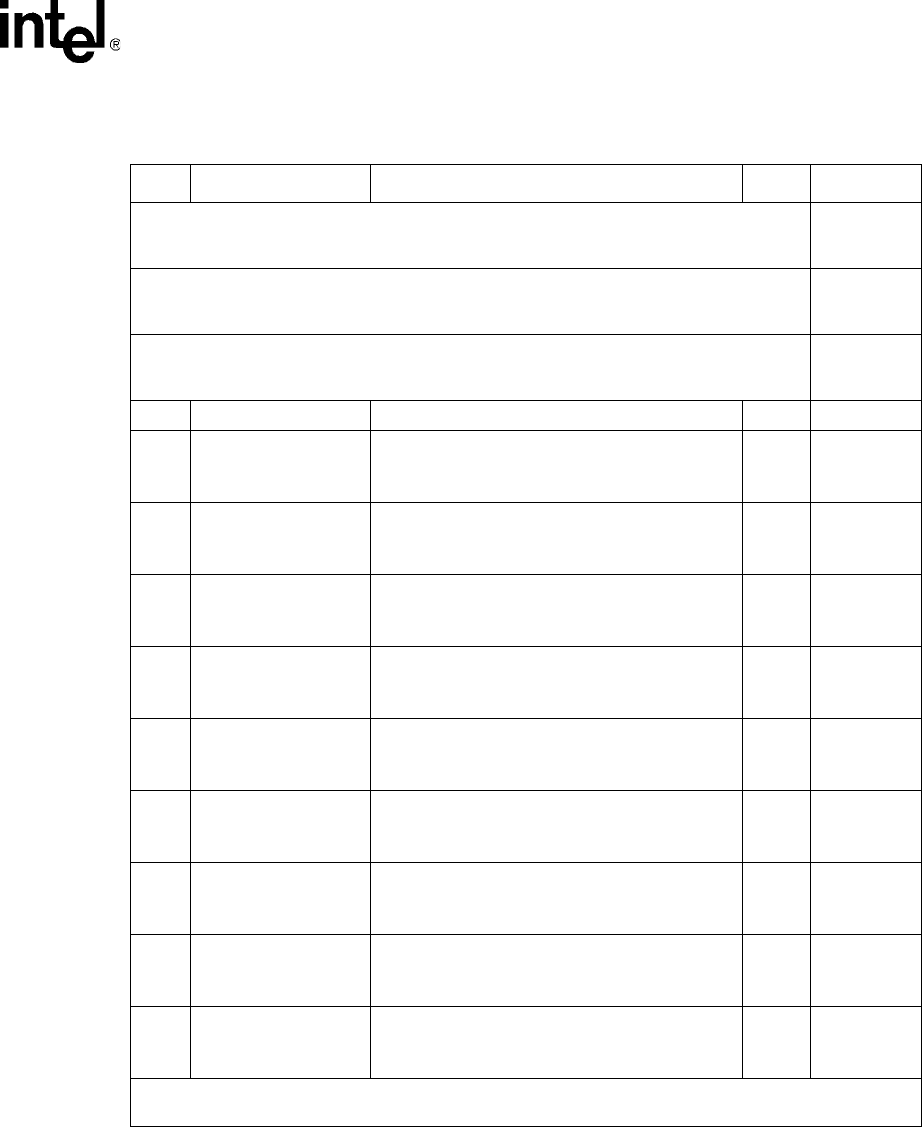

Table 135. TX FIFO Overflow/Underflow/Out of Sequence Event ($0x61E) (Sheet 1 of 2)

Bit Name Description Type

1

Default

Register Description: TX FIFO Out of Sequence Event:

These register bits provide status information, and indicate if out-of-sequence data has been

received. The bit position equals the port number + 8. These bits are cleared on Read.

0x0

Register Description: TX FIFO Underflow Event:

This register provides a status that a FIFO Empty situation has occurred (for example, a FIFO

under-run). The bit position equals the port number + 4. This register is cleared on Read.

0x0

Register Description: TX FIFO Overflow Event:

This register provides a status that a FIFO full situation has occurred (for example, a FIFO

overflow). The bit position equals the port number. This register is cleared on Read.

0x0

31:12 Reserved Reserved RO 0x00000

11 FOSE3

Port 3

0 = FIFO out of sequence event did not occur

1 = FIFO out of sequence event occurred

R0

10 FOSE2

Port 2

0 = FIFO out of sequence event did not occur

1 = FIFO out of sequence event occurred

R0

9 FOSE1

Port 1

0 = FIFO out of sequence event did not occur

1 = FIFO out of sequence event occurred

R0

8 FOSE0

Port 0

0 = FIFO out of sequence event did not occur

1 = FIFO out of sequence event occurred

R0

7FUE3

Port 3

0 = FIFO underflow event did not occur

1 = FIFO underflow event occurred

R0

6FUE2

Port 2

0 = FIFO underflow event did not occur

1 = FIFO underflow event occurred

R0

5FUE1

Port 1

0 = FIFO underflow event did not occur

1 = FIFO underflow event occurred

R0

4FUE0

Port 0

0 = FIFO underflow event did not occur

1 = FIFO underflow event occurred

R0

3FOE3

Port 3

0 = FIFO overflow event did not occur

1 = FIFO overflow event occurred

R0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write