IXF1104 4-Port Gigabit Ethernet Media Access Controller

158 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

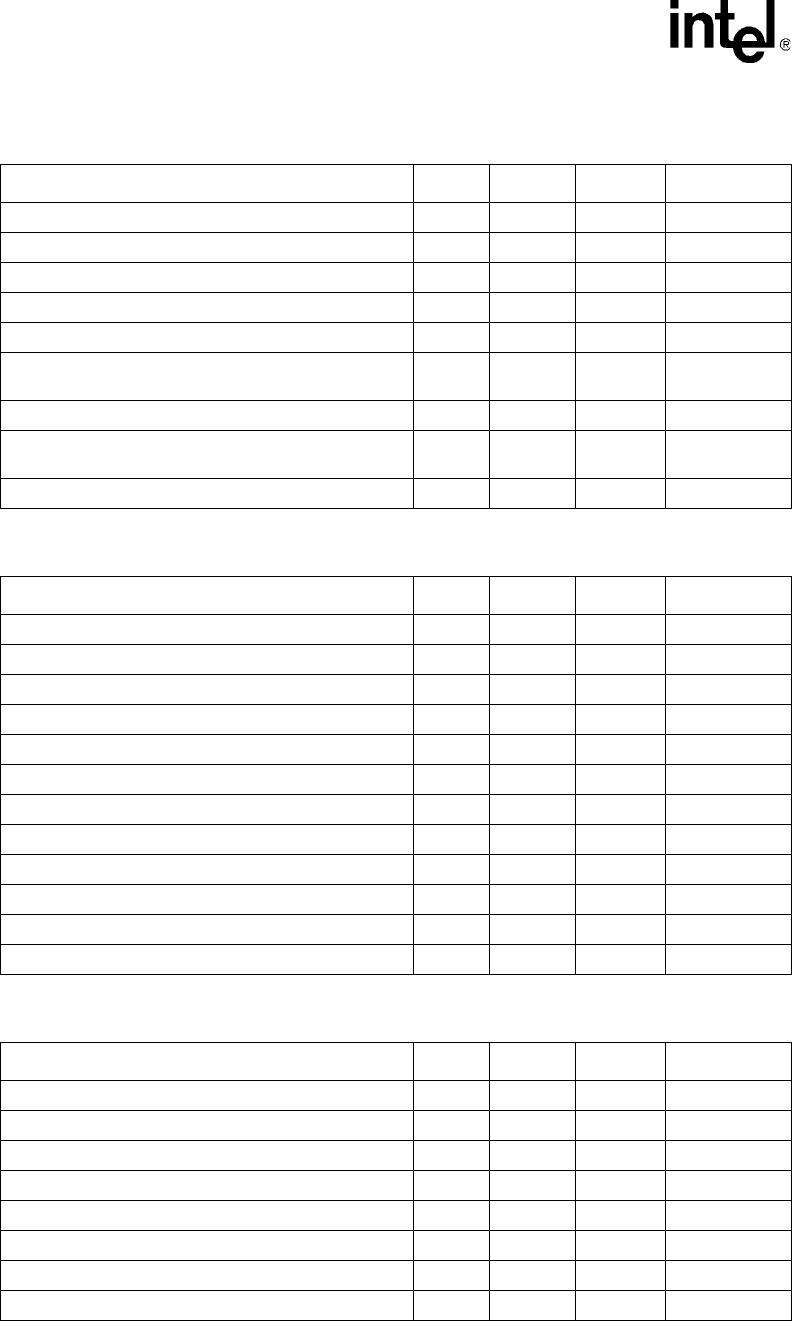

Table 62. PHY Autoscan Registers ($ Port Index + Offset)

Register Bit Size Mode

1

Ref Page Offset

“PHY Control ($ Port Index + 0x60)” 32 RO 180 0x60

“PHY Status ($ Port Index + 0x61)” 32 RO 181 0x61

“PHY Identification 1 ($ Port Index + 0x62)” 32 RO 182 0x62

“PHY Identification 2 ($ Port Index + 0x63)” 32 RO 182 0x63

“Auto-Negotiation Advertisement ($ Port Index + 0x64)” 32 RO 183 0x64

“Auto-Negotiation Link Partner Base Page Ability ($ Port

Index + 0x65)”

32 RO 184 0x65

“Auto-Negotiation Expansion ($ Port Index + 0x66)” 32 RO 185 0x66

“Auto-Negotiation Next Page Transmit ($ Port Index +

0x67)”

32 RO 186 0x67

Reserved 32 RO – 0x68 - 0x6F

Table 63. Global Status and Configuration Registers ($ 0x500 - 0X50C)

Register Bit Size Mode

1

Ref Page Address

“Port Enable ($0x500)” 32 R/W 187 0x500

“Interface Mode ($0x501)” 32 R/W 187 0x501

“Link LED Enable ($0x502)” 32 R/W 188 0x502

Reserved 32 RO – 0x503 - 0x504

“MAC Soft Reset ($0x505)” 32 R/W 188 0x505

“MDIO Soft Reset ($0x506)” 32 R/W 189 0x506

Reserved 32 RO – 0x507

“CPU Interface ($0x508)” 32 R/W 189 0x508

“LED Control ($0x509)” 32 R/W 189 0x509

“LED Flash Rate ($0x50A)” 32 R/W 190 0x50A

“LED Fault Disable ($0x50B)” 32 R/W 190 0x50B

“JTAG ID ($0x50C)” 32 R 191 0x50C

Table 64. RX FIFO Registers ($ 0x580 - 0x5BF) (Sheet 1 of 2)

Register Bit Size Mode

1

Ref Page Address

“RX FIFO High Watermark Port 0 ($0x580)” 32 R/W 192 0x580

“RX FIFO High Watermark Port 1 ($0x581)” 32 R/W 192 0x581

“RX FIFO High Watermark Port 2 ($0x582)” 32 R/W 192 0x582

“RX FIFO High Watermark Port 3 ($0x583)” 32 R/W 193 0x583

Reserved 32 RO – 0x584 - 0x589

“RX FIFO Low Watermark Port 0 ($0x58A)” 32 R/W 193 0x58A

“RX FIFO Low Watermark Port 1 ($0x58B)” 32 R/W 193 0x58B

“RX FIFO Low Watermark Port 2 ($0x58C)” 32 R/W 194 0x58C