IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 167

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

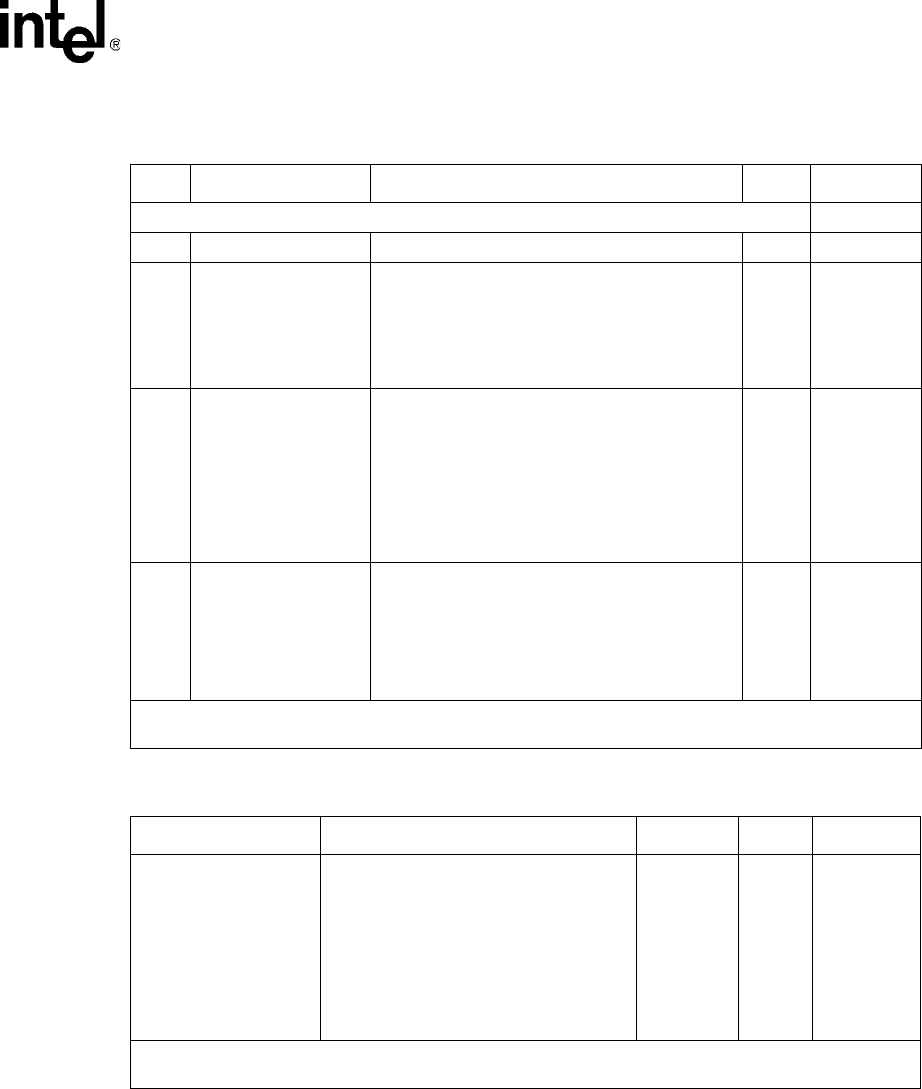

Table 84. FC Enable ($ Port_Index + 0x12)

Bit Name Description Type

1

Default

Register Description:

Indicates which flow control mode is used for the RX and TX MAC. 0x00000007

31:3 Reserved Reserved R 0x00000000

2TX HDFC

When TX HDFC is enabled (half-duplex mode

only), the MAC generates deliberate collisions on

incoming packets when the RX FIFO occupancy

crosses the High Watermark (flow control).

0 = Disable TX half-duplex flow control

1 = Enable TX half-duplex flow control

R/W 1

1TX FDFC

0 = Disable TX full-duplex flow control [the MAC

will not generate internally any flow control

frames based on the RX FIFO watermarks or

the Transmit Pause Control interface

1 = Enable TX full-duplex flow control [enables

the MAC to send flow control frames to the

link partner based on the RX FIFO

programmable watermarks or the Transmit

Pause Control interface]

R/W 1

0RX FDFC

0 = Disable RX full-duplex flow control [the MAC

will not respond to flow control frames sent to

it by the link partner]

1 = Enable RX full-duplex flow control [MAC will

respond to flow control frames sent by the link

partner and will stop packet transmission for

the time specified in the flow control frame]

R/W 1

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 85. FC Back Pressure Length ($ Port_Index + 0x13)

Name Description Address Type

1

Default

FC Back Pressure

Length

This register sets number the byte cycles

for which the collision has to be applied.

The 6-bit configuration holds the value in

bytes, which applies to the minimum

length/duration of back pressure in half-

duplex mode. Flow control in the receive

path is executed by deliberately colliding

the incoming packets in half-duplex mode.

Register bits 5:0 are used alone.

Port Add +

0x13

R/W 0x0000000C

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write