IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

Datasheet 85

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

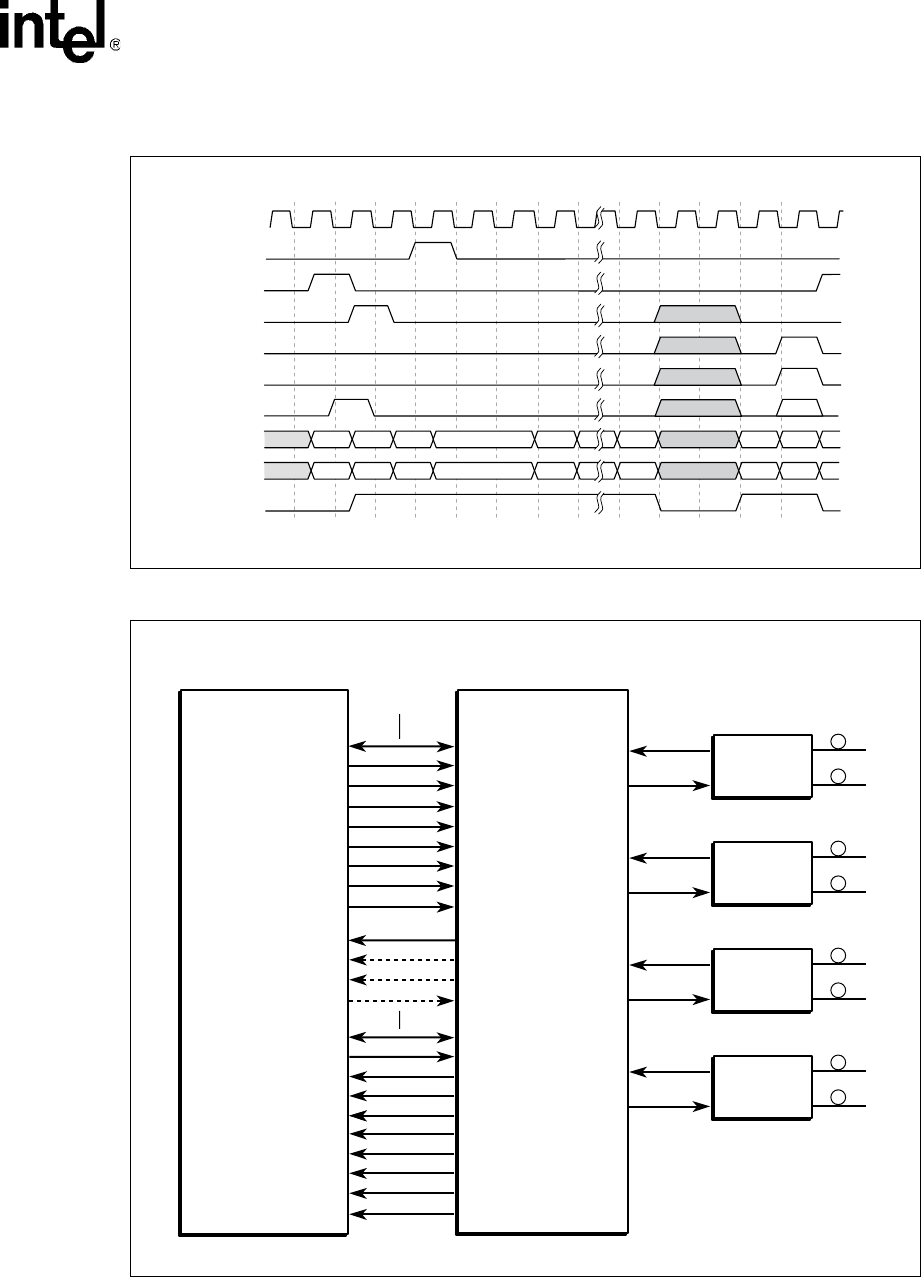

Figure 12. MPHY Receive Logical Timing

Figure 13. MPHY 32-Bit Interface

B3217-01

TFCLK

RENB

RSX

RSOP

REOP

RERR

RMOD[1:0]

RDAT[31:0]

RPRTY

RVAL

0000 B1-B4 B5-B8 B9-B12 B13-B16 B45-B48 B52-B55 B56-B57 B0001

B0660-02

TFCLK

TENB

TDAT[31:0]

TPRTY

TERR

TSX

TSOP

TEOP

Network Processor

SPI3 Bus

IXF1104 MPHY

Mode

Transceiver

TFCLK

TENB_0

TDAT[31:0]

TPRTY_0

TMOD[1:0]

TMOD[1:0]

RMOD[1:0]

RMOD[1:0]

TERR_0

TSX

TSOP_0

TEOP_0

RFCLK

RENB

RDAT[31:0]

RPRTY

RPRTY

RVAL

RERR

RSX

RSOP

REOP

RPRTY_0

RFCLK

RENB_0

RDAT[31:0]

RVAL_0

RERR_0

RSX

RSOP_0

REOP_0

DTPA_0:3

STPA

PTPA

TADR[1:0]

DTPA_0:3

STPA

PTPA

TADR[1:0]

Transceiver

Transceiver

Transceiver

Line-Side Interface

Port 0

Port 1

Port 3

Port 2