IXF1104 4-Port Gigabit Ethernet Media Access Controller

42 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

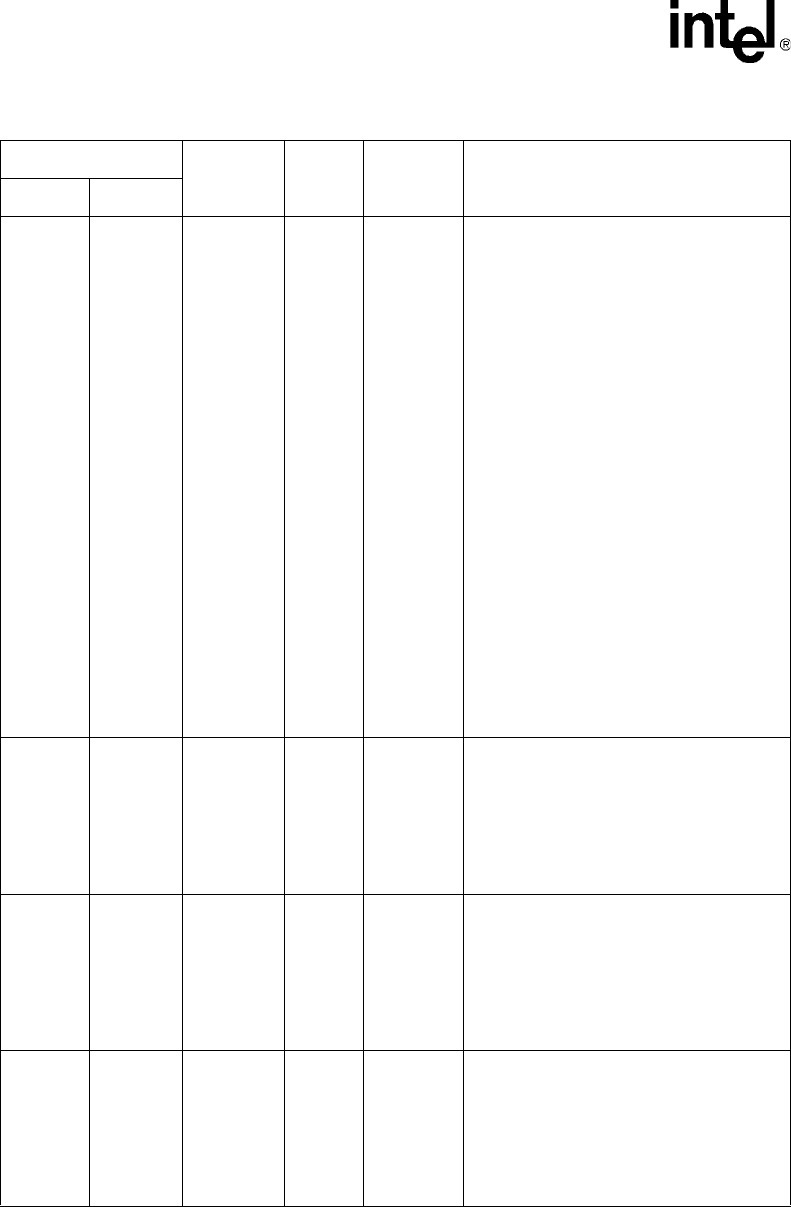

PTPA PTPA B11 Output

3.3 V

LVTTL

Polled-PHY Transmit Packet Available.

PTPA allows the polling of the port selected

by the TADR address bus.

When High, PTPA indicates that the amount

of data in the TX FIFO is below the TX FIFO

High watermark. When the High watermark

is crossed, PTPA transitions Low to indicate

that the TX FIFO is almost full. It stays Low

until the amount data in the TX FIFO goes

back below the TX FIFO Low watermark. At

this point, PTPA transitions High to indicate

that the programmed number of bytes are

now available for data transfers.

NOTE: For more information, see

Table 132 “TX FIFO High

Watermark Ports 0 - 3 ($0x600 –

0x603)” on page 202 and Table 133

“TX FIFO Low Watermark Register

Ports 0 - 3 ($0x60A – 0x60D)” on

page 203.

The port reported by PTPA is updated on

the following rising edge of TFCLK after the

port address on TADR is sampled by the

PHY device.

PTPA is updated on the rising edge of

TFCLK.

RDAT31

RDAT30

RDAT29

RDAT28

RDAT27

RDAT26

RDAT25

RDAT24

RDAT7_3

RDAT6_3

RDAT5_3

RDAT4_3

RDAT3_3

RDAT2_3

RDAT1_3

RDAT0_3

F24

G24

G23

G22

G21

G20

G19

G18

Output

3.3 V

LVTTL

Receive Data Bus.

RDAT carries payload data and in-band

addresses from the IXF1104.

Mode

32-bit Multi-PHY

4 x 8 Single-PHY

Bits

[31:24]

[7:0] for port 3

RDAT23

RDAT22

RDAT21

RDAT20

RDAT19

RDAT18

RDAT17

RDAT16

RDAT7_2

RDAT6_2

RDAT5_2

RDAT4_2

RDAT3_2

RDAT2_2

RDAT1_2

RDAT0_2

E21

E22

D22

C22

C21

C20

B22

B20

Output

3.3 V

LVTTL

Receive Data Bus.

RDAT carries payload data and in-band

addresses from the IXF1104.

Mode

32-bit Multi-PHY

4 x 8 Single-PHY

Bits

[23:16]

[7:0] for port 2

RDAT15

RDAT14

RDAT13

RDAT12

RDAT11

RDAT10

RDAT9

RDAT8

RDAT7_1

RDAT6_1

RDAT5_1

RDAT4_1

RDAT3_1

RDAT2_1

RDAT1_1

RDAT0_1

F18

E18

E17

F16

E16

D16

C17

A17

Output

3.3 V

LVTTL

Receive Data Bus.

RDAT carries payload data and in-band

addresses from the IXF1104.

Mode

32-bit Multi-PHY

4 x 8 Single-PHY

Bits

[15:8]

[7:0] for port 1

Table 3. SPI3 Interface Signal Descriptions (Sheet 5 of 8)

Signal Name

Ball

Designator

Type Standard Description

MPHY SPHY