IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

68 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

When the CRC Error Pass Filter bit = 0 (“RX Packet Filter Control ($ Port_Index + 0x19)”), it

takes precedence over the other filter bits. Any packet (Pause, Unicast, Multicast or Broadcast

packet) with a CRC error will be marked as a bad frame when the CRC Error Pass Filter bit = 0.

5.1.1.4 CRC Error Detection

Frames received by the MAC are checked for a correct CRC. When an incorrect CRC is detected

on a received frame, the RX FCSError RMON statistic counter is incremented for each CRC

errored frame. Received frames with CRC errors may optionally be dropped in the RX FIFO (refer

to Section 5.1.1.3.6, “Filter CRC Error Packets” on page 67). Otherwise, the frames are sent to the

SPI3 interface and may be dropped by the switch or system controller.

Frames transmitted by the MAC are also checked for correct CRC. When an incorrect CRC is

detected on a transmitted frame, the TX CRCError RMON statistic counter is incremented for each

incorrect frame.

5.1.2 Flow Control

Flow Control is an IEEE 802.3x-defined mechanism for one network node to request that its link

partner take a temporary “Pause” in packet transmission. This allows the requesting network node

to prevent FIFO overruns and dropped packets, by managing incoming traffic to fit its available

memory. The temporary pause allows the device to process packets already received or in transit,

thus freeing up the FIFO space allocated to those packets.

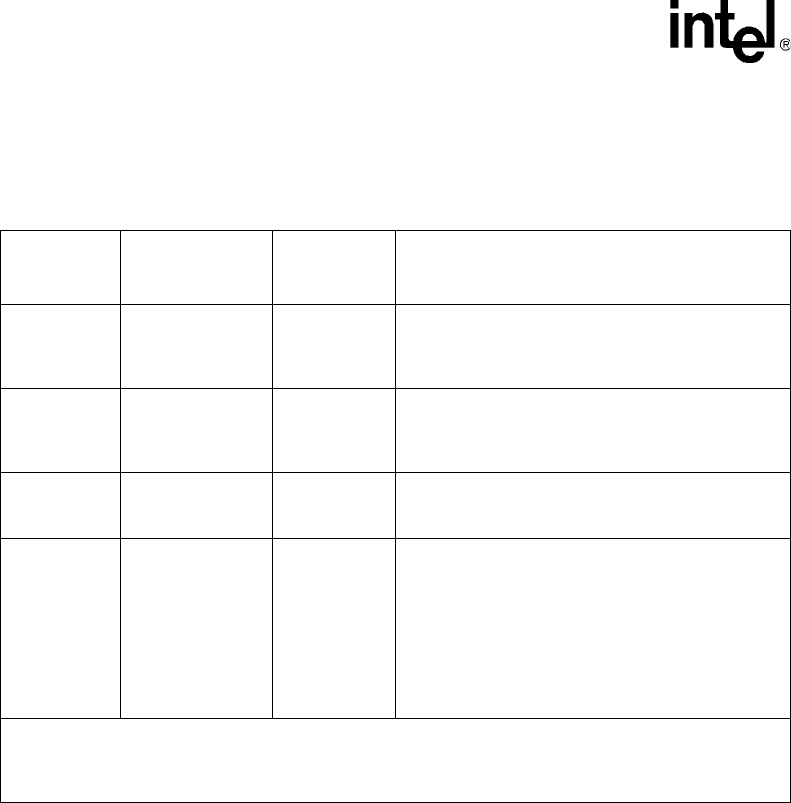

Table 22. CRC Errored Packets Drop Enable Behavior

CRC Error

Pass

1

RX FIFO Errored-

Frame Drop

Enable

2

RERR

Enable

3

Actions

1xx

When CRC Errored PASS = 1, CRC errored packets

are not filtered and are passed to the SPI3 interface.

They are not marked as bad, cannot be dropped, and

cannot be signaled with RERR.

001

Packets are marked as bad but not dropped in the

RX FIFO. These packets are sent to the SPI3

interface, and are signaled with an RERR to the

switch or Network Processor.

000

Packets are marked as bad but not dropped in the

RX FIFO. These packets are sent to the SPI3

interface, and are not signaled with an RERR.

01x

CRC errored packets are marked as bad, dropped in

the RX FIFO, and never appear at the SPI3 interface.

NOTE: Packet sizes above the RX FIFO Transfer

Threshold (see Table 128 through Table 131)

cannot be dropped in the RX FIFO and are

passed to the SPI3 interface. These packets

can optionally be signaled with RERR on the

SPI3 interface if the RERR Enable bit = 1.

1. See Table 91 “RX Packet Filter Control ($ Port_Index + 0x19)” on page 171.

2. See Table 123 “RX FIFO Errored Frame Drop Enable ($0x59F)” on page 195.

3. See Table 147 “SPI3 Receive Configuration ($0x701)” on page 214.

NOTE: x = “DON’T CARE”