IXF1104 4-Port Gigabit Ethernet Media Access Controller

210 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

8.4.8 MDIO Register Overview

Table 142 through Table 145 provide an overview of the MDIO registers.

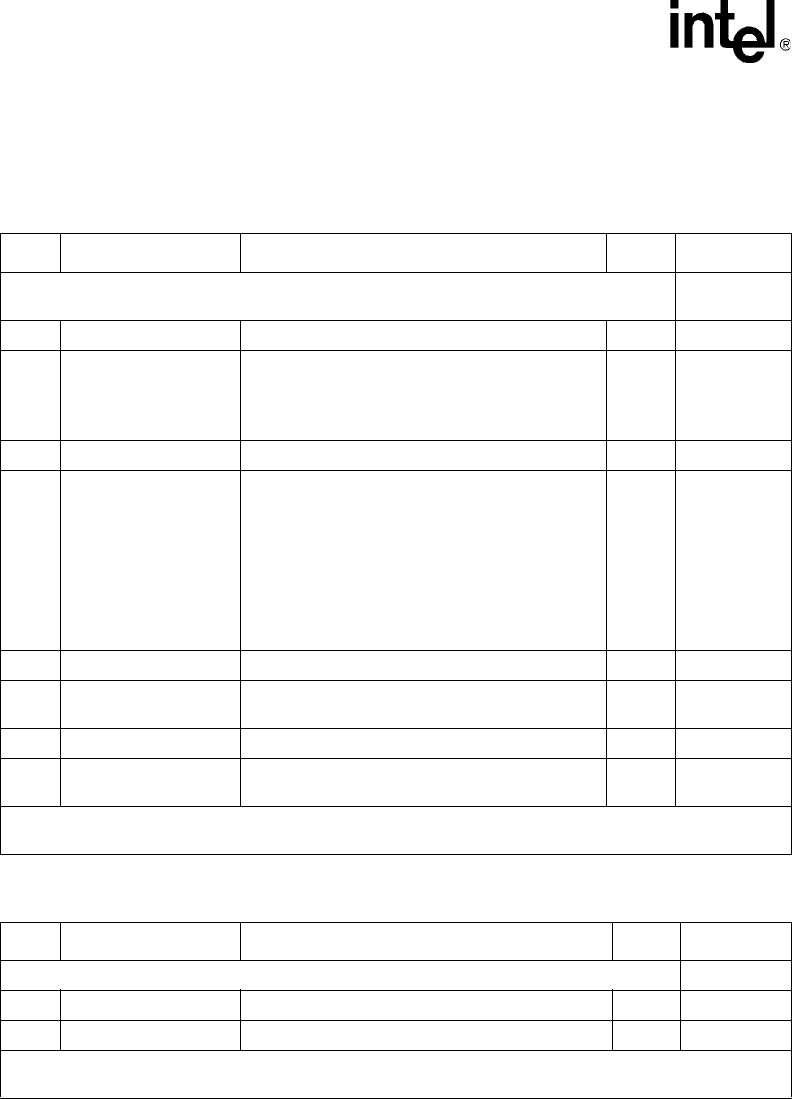

Table 142. MDIO Single Command ($0x680)

Bit Name Description Type

1

Default

Register Description:

Gives the CPU the ability to perform single MDIO read and write

accesses to the external PHY for ports that are configured in copper mode.

0x00010000

31:21 Reserved Reserved RO 00000000000

20 MDIO Command

Performs the MDIO operation. Cleared when

done.

0 = MDIO ready, operation complete

1 = Perform operation

R/W 0

19:18 Reserved Reserved RO 00

17:16 OP Code

MDIO Op Code; two bits identify operation to be

performed:

00 =Reserved

01 =Write operation (as defined in IEEE 802.3,

clause 22.2.4.5)

10 =Read operation (as defined in IEEE 802.3,

clause 22.2.4.5)

11 = Reserved

R/W 01

15:10 Reserved Reserved RO 000000

9:8 PHY Address

Sets bits 1:0 of the external PHY address. Bits 4:2

of the PHY address are fixed at 000.

R/W 00

7:5 Reserved Reserved RO 000

4:0 REG Address

Five-bit address to one among 32 registers in an

addressed PHY device.

R/W 00000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 143. MDIO Single Read and Write Data ($0x681)

Bit Name Description Type

1

Default

Register Description:

MDIO read and write data. 0x00000000

31:16 MDIO Read Data MDIO Read data from external device. RO 0x0000

15:0 MDIO Write Data MDIO Write data from external device. R/W 0x0000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write