IXF1104 4-Port Gigabit Ethernet Media Access Controller

198 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

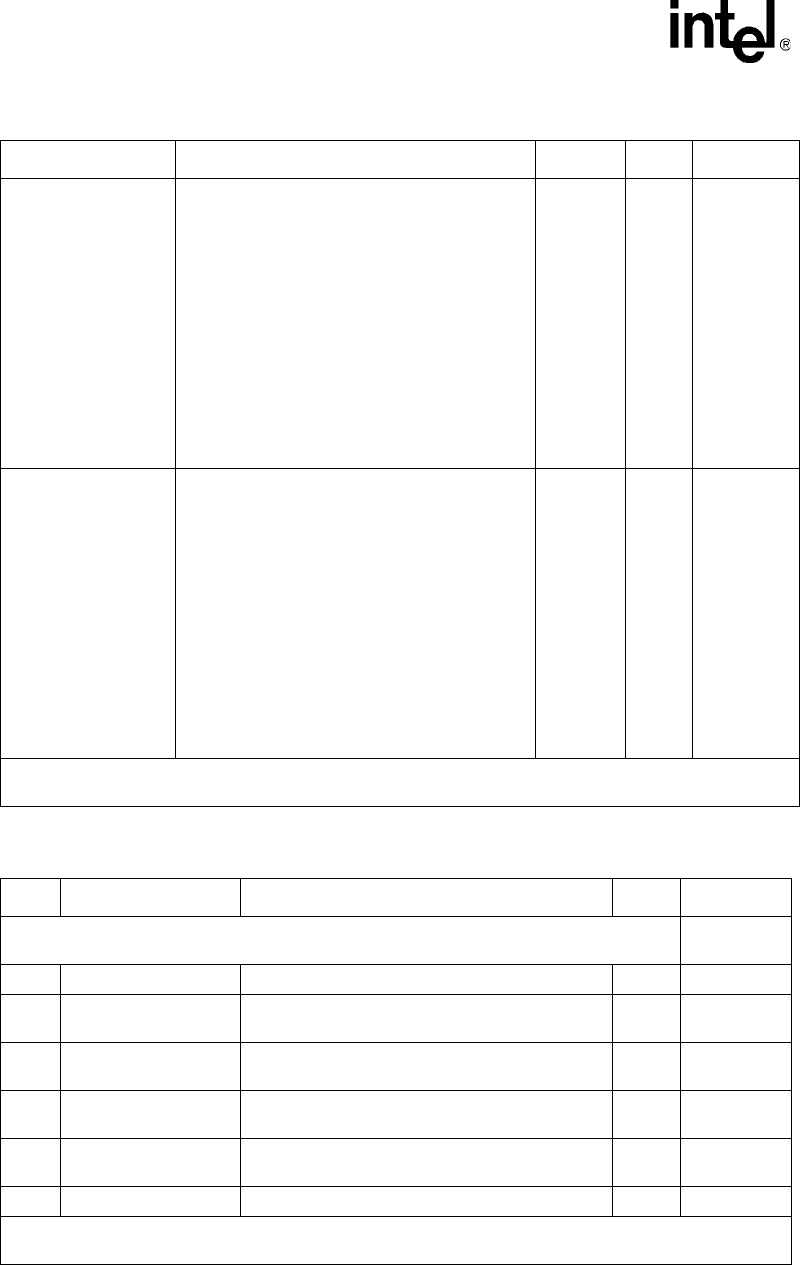

RX FIFO Errored

Frame Drop Counter

on Port 2

This register counts all frames dropped from the

RX FIFO for port 2 by meeting one of the

following conditions:

• Frames are removed in conjunction

with the“RX FIFO Errored Frame

Drop Enable ($0x59F)” and the “RX

Packet Filter Control ($ Port_Index +

0x19)”.

• Frames are greater than the “Max

Frame Size (Addr: Port_Index +

0x0F)”.

This register is cleared on Read.

0x5A4 R 0x00000000

RX FIFO Errored

Frame Drop Counter

on Port 3

This register counts all frames dropped from the

RX FIFO for port 3 by meeting one of the

following conditions:

• Frames are removed in conjunction

with the“RX FIFO Errored Frame

Drop Enable ($0x59F)” and the “RX

Packet Filter Control ($ Port_Index +

0x19)”.

• Frames are greater than the “Max

Frame Size (Addr: Port_Index +

0x0F)”.

This register is cleared on Read.

0x5A5 R 0x00000000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write

Table 126. RX FIFO SPI3 Loopback Enable for Ports 0 - 3 ($0x5B2)

Bit Name Description Type

1

Default

Register Description:

Enables the TX SPI3 port to send packets into the RX_FIFO instead of

into the TX FIFO, creating a SPI3 loopback.

0x00000000

31:12 Reserved Reserved RO 0x00000

11

SPI3 loopback enable

for Port 3

0 = Disabled

1 = Enabled

R/W 0x0

10

SPI3 loopback enable

for Port 2

0 = Disabled

1 = Enabled

R/W 0x0

9

SPI3 loopback enable

for Port 1

0 = Disabled

1 = Enabled

R/W 0x0

8

SPI3 loopback enable

for Port 0

0 = Disabled

1 = Enabled

R/W 0x0

7:0 Reserved Write as 0, ignore on Read. R/W 0x00

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 125. RX FIFO Errored Frame Drop Counter Ports 0 - 3 ($0x5A2 - 0x5A5) (Sheet 2 of 2)

Name Description Address Type Default