IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 199

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

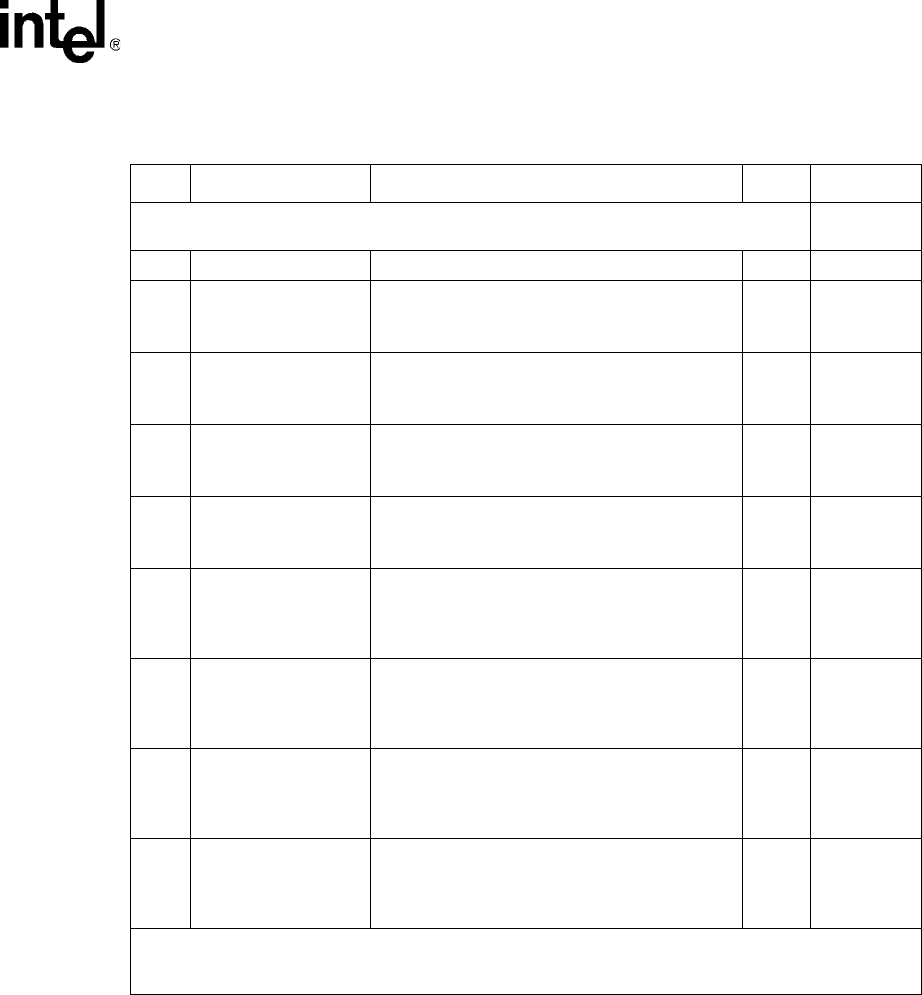

Table 127. RX FIFO Padding and CRC Strip Enable ($0x5B3)

Bit Name Description Type

1

Default

Register Description:

This control register enables to pre-pend every packet with two extra

bytes and also enables the CRC stripping of a packet.

0x00000000

31:8 Reserved Reserved RO 0x000000

7

CRC Stripping Enable

for Port 3

CRC stripping is enabled for Port 3.

0 = Disabled

1 = Enabled

R/W 0

6

CRC Stripping Enable

for Port 2

CRC stripping is enabled for Port 2.

0 = Disabled

1 = Enabled

R/W 0

5

CRC Stripping Enable

for Port 1

CRC stripping is enabled for Port 1.

0 = Disabled

1 = Enabled

R/W 0

4

CRC Stripping Enable

for Port 0

CRC stripping is enabled for Port 0.

0 = Pre-pending Disabled

1 = Pre-pending Enabled

R/W 0

3

Pre-pending Enable

2

Port 3

Enables pre-pending of two bytes at the start of

every packet – Port 3.

0 = Disabled

1 = Enabled

R/W 0

2

Pre-pending Enable

2

Port 2

Enables pre-pending of two bytes at the start of

every packet – Port 2.

0 = Disabled

1 = Enabled

R/W 0

1

Pre-pending Enable

2

Port 1

Enables pre-pending of two bytes at the start of

every packet – Port 1.

0 = Disabled

1 = Enabled

R/W 0

0

Pre-pending Enable

2

Port 0

Enables pre-pending of two bytes at the start of

every packet – Port 0.

0 = Disabled

1 = Enabled

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

2. Pre-pending should not be enabled in loopback mode.