IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 175

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

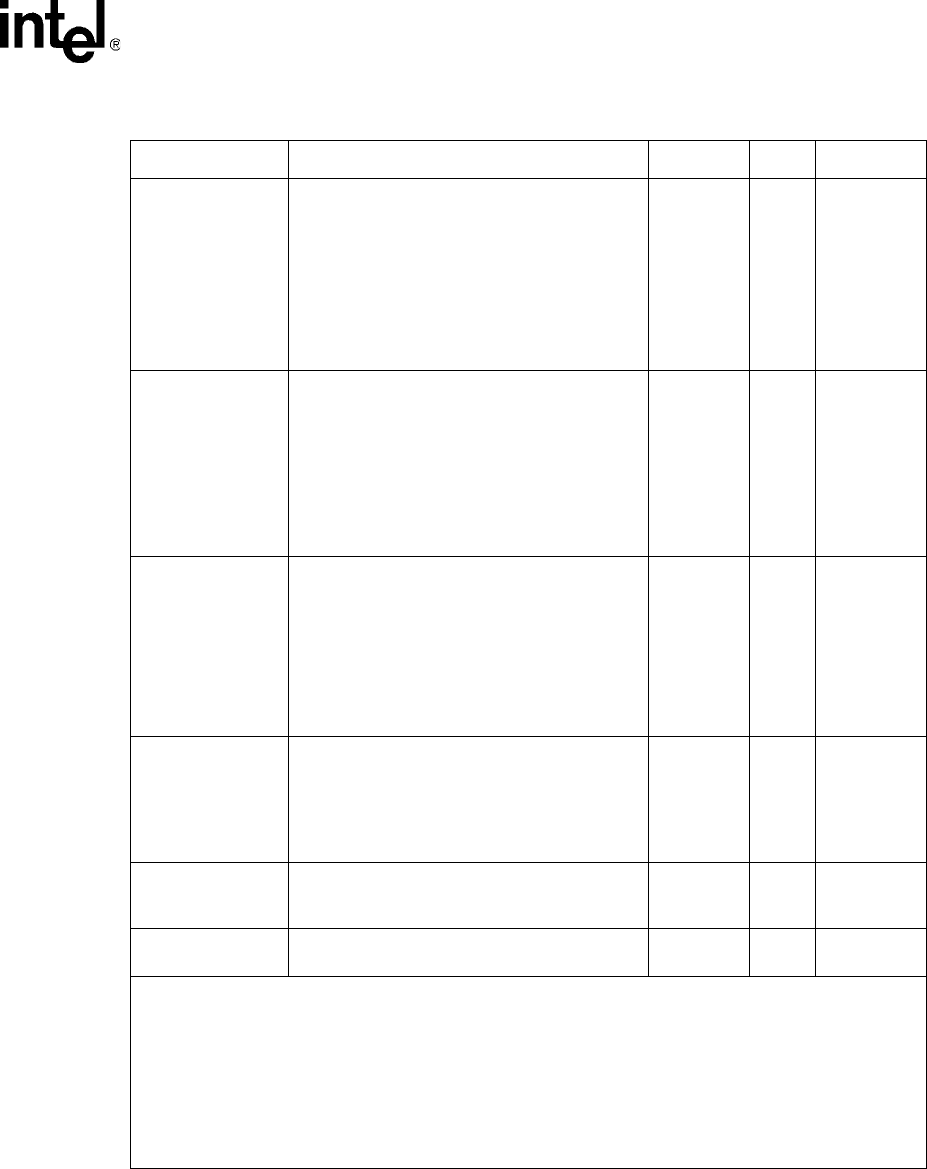

RxAlignErrors

3

Frames with a legal frame size, but containing

less than eight additional bits. This occurs when

the frame is not byte aligned. The CRC of the

frame is wrong when the additional bits are

stripped. If the CRC is OK, then the frame is not

counted but treated as an OK frame. This

counter increments in 10 Mbps or 100 Mbps

RGMII mode only.

NOTE: This counter increments in 10 or 100

Mbps RGMII mode only.

Port_Index

+ 0x2F

R 0x00000000

RxLongErrors

2

Frames bigger than the maximum allowed, with

both OK CRC and the integral number of octets.

Default maximum allowed is 1518 bytes

untagged and 1522 bytes tagged, but the value

can be changed by a register.

Frames bigger than the larger of

2*maxframesize and 50,000 bits are not counted

here, but they are counted in the VeryLongError

counter.

Port_Index

+ 0x30

R 0x00000000

RxJabberErrors

Frames bigger than the maximum allowed, with

either a bad CRC or a non-integral number of

octets. The default maximum allowed is 1518

bytes untagged and 1522 bytes tagged, but the

value can be changed by a register.

Frames bigger than the larger of

2*maxframesize and 50,000 bits are not counted

here, but they are counted in the VeryLongError

counter.

Port_Index

+ 0x31

R 0x00000000

RxPauseMacContr

olReceivedCounter

Number of Pause MAC control frames received.

This statistic register increments on any valid 64-

byte pause frame with a valid CRC and also

increments on a 64-byte pause frame with an

invalid CRC if bit 5 of the “RX Packet Filter

Control ($ Port_Index + 0x19)” is set to 1.

Port_Index

+ 0x32

R 0x00000000

RxUnknownMac

ControlFrame

Counter

Number of MAC control frames received with an

op code different from 0001 (Pause).

Port_Index

+ 0x33

R 0x00000000

RxVeryLongErrors

2

Frames bigger than the larger of

2*maxframesize and 50,000 bits

Port_Index

+ 0x34

R 0x00000000

Table 93. MAC RX Statistics ($ Port_Index + 0x20 – + 0x39) (Sheet 3 of 4)

Name Description Address Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write

2. When sending in large frames, the counters can only handle certain limits. The behavior of the LongErrors

and VeryLongErrors counters is as follows: VeryLongErrors counts frames that are 2*maxframesize,

dependent upon where maxframesize is set. If maxframesize sets greater than half of the available count in

RxOctetsBad (2^14-1), VeryLongErrors is never incremented, but LongErrors is incremented. This is due to

a limitation in the counter size, which means that an accurate count will not occur in the RxOctetsBAD

counter if the frame is larger than 2^14-1.

3. This register is relevant only when configured for copper operation.

4. This register is relevant only when configured for fiber operation (line side interface is SerDes).