IXF1104 4-Port Gigabit Ethernet Media Access Controller

200 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

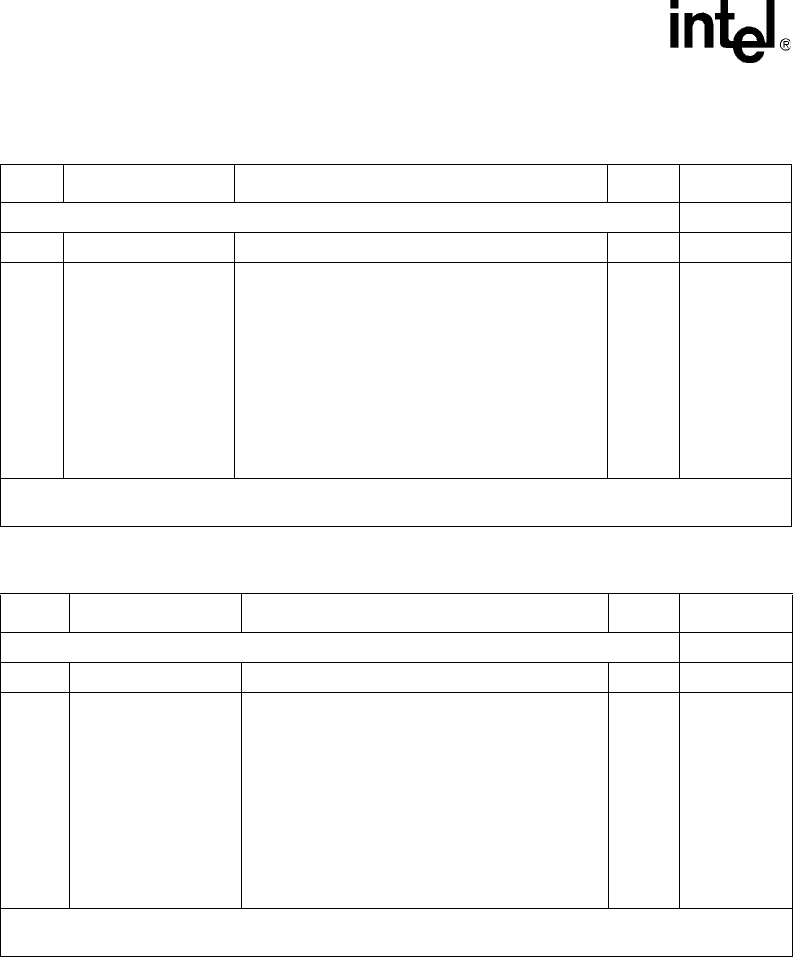

Table 128. RX FIFO Transfer Threshold Port 0 ($0x5B8)

Bit Name Description Type Default

Register Description:

RX FIFO transfer threshold for port 0 in 8-byte location. 0x000000BE

31:12 Reserved Reserved RO 0x00000

11:0

RX FIFO Transfer

Threshold - Port 0

RX FIFO transfer threshold for port 0. This must

be less than the RX FIFO High water mark.

User definable control register that sets the

threshold where a packet starts transitioning to the

SPI3 interface from the RX FIFO before the EOP

is received. Packets received in the RX FIFO

below this threshold are treated as store and

forward.

NOTE: Do not program the RX FIFO transfer

threshold below a setting of 0xBE

(1520bytes).

R/W 0x0BE

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 129. RX FIFO Transfer Threshold Port 1 ($0x5B9)

Bit Name Description Type Default

Register Description:

RX FIFO transfer threshold for port 1in 8-byte location. 0x000000BE

31:12 Reserved Reserved RO 0x00000

11:0

RX FIFO Transfer

Threshold - Port 1

RX FIFO transfer threshold for port 1. This must

be less than the RX FIFO High watermark.

User definable control register that sets the

threshold where a packet starts transitioning to

the SPI3 interface from the RX FIFO before the

EOP is received. Packets received in the RX

FIFO below this threshold are treated as store

and forward.

NOTE: Do not program the RX FIFO transfer

threshold below a setting of 0xBE

(1520bytes).

R/W 0x0BE

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write