IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 183

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

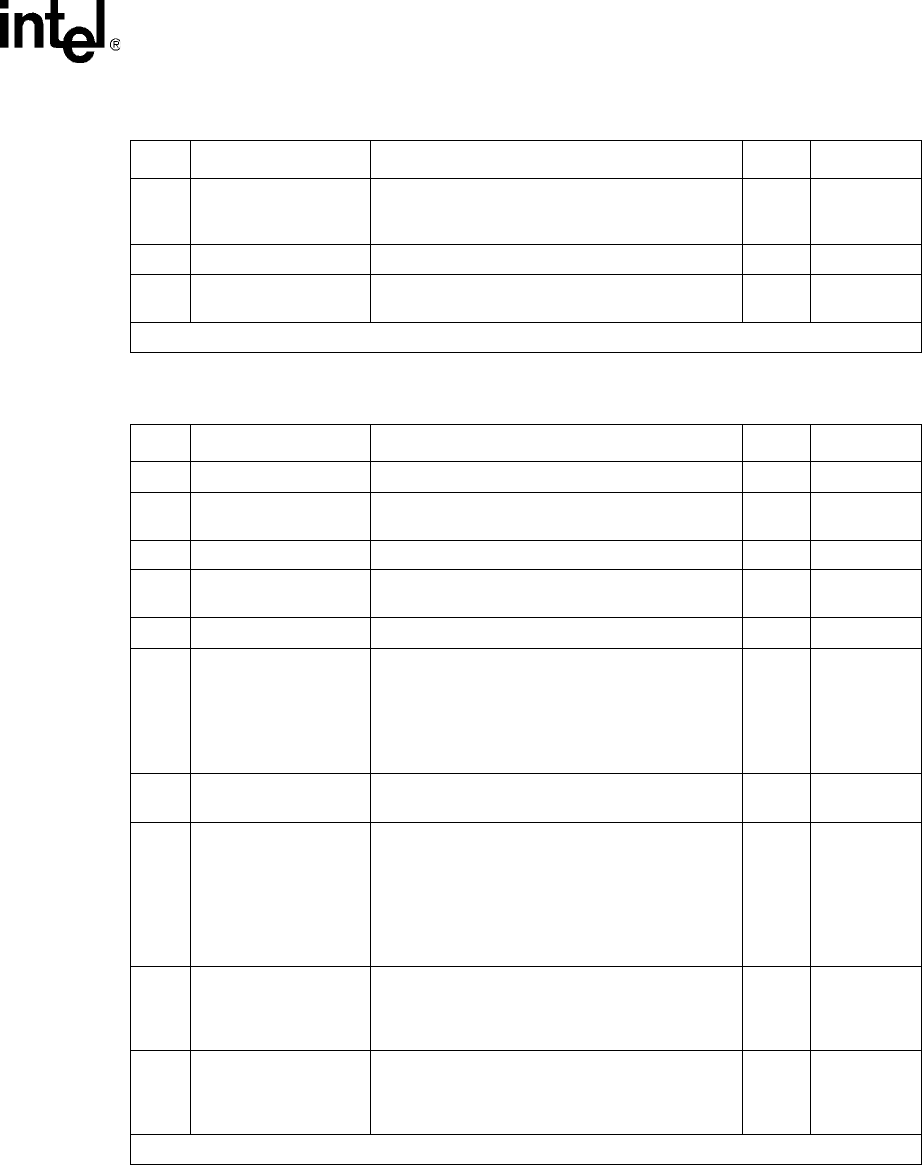

15:10 PHY ID Number

The PHY identifier is composed of register bits

24:19 of the OUI (Organizationally Unique

Identifier)

RO 011110

9:4 Manufacturer’s Model Six bits containing the manufacturer’s part number RO 010000

3:0

Manufacturer’s

Revision Number

Four bits containing the manufacturer’s revision

number

RO 0000

Table 99. Auto-Negotiation Advertisement ($ Port Index + 0x64) (Sheet 1 of 2)

Bit Name Description Type

1

Default

31:16 Reserved Reserved RO 0

15 Next Page

0 =

1 = Manual control of Next Page (software)

RO 0

14 Reserved Reserved RO 0

13 Remote Fault

0 = No remote fault

1 = Remote fault

RO 0

12 Reserved Reserved RO 0

11 ASM_DIR

Advertise Asymmetric Pause Direction register bit.

This register bit is used in conjunction with Pause

(Register bit 4.10)

0 = Link partner is not capable of asymmetric

pause

1 = Link partner is capable of asymmetric pause

RO 1

10 Pause

Advertise to link partner that Pause operation is

desired (IEEE 802.3x Standard)

RO 0

9 100BASE-T4

0 = 100BASE-T4 capability is not available

1 = 100BASE-T4 capability is available

The IXF1104 does not support 100BASE-T4, but

allows this register bit to be set to advertise in

auto-negotiation sequence for 100BASE-T4

operation. If this capability is desired, an external

100BASE-T4 transceiver can be switched in.

RO 0

8

100BASE-TX

Full-Duplex

0 = DTE is not 100BASE-TX, full-duplex mode

capable

1 = DTE is 100BASE-TX, full-duplex mode

capable

RO 1

7

100BASE-TX

Half-Duplex

0 = DTE is not 100BASE-TX, half-duplex mode

capable

1 = DTE is 100BASE-TX, half-duplex mode

capable

RO 1

1. RO = Read Only; RR = Clear on Read; W = Write; R/W = Read/Write

Table 98. PHY Identification 2 ($ Port Index + 0x63) (Sheet 2 of 2)

Bit Name Description Type

1

Default

1. RO = Read Only; RR = Clear on Read; W = Write; R/W = Read/Write