IXF1104 Quad-Port 10/100/1000 Mbps Ethernet Media Access Controller

Datasheet 71

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

An IEEE 802.3 MAC PAUSE frame is identified by detecting all of the following:

• OpCode of 00-01

• Length/Type field of 88-08

• DA matching the unique multicast address (01-80-C2-00-00-01)

XOFF. A PAUSE frame informs the link partner to halt transmission for a specified length of time.

The PauseLength octets specify the duration of the no-transmit period. If this time is greater than

zero, the link partner must stop sending any further packets until this time has elapsed. This is

referred to as XOFF.

XON. The MAC continues to transmit PAUSE frames with the specified Pause Length as long as

the FIFO level exceeds the threshold. If the FIFO level falls below the threshold before the Pause

Length time expires, the MAC sends another PAUSE frame with the Pause Length time specified

as zero. This is referred to as XON and informs the link partner to resume normal transmission of

packets.

5.1.2.1.2 Pause Settings

The MAC must send PAUSE frames repeatedly to maintain the link partner in a Pause state. The

following two inter-related variables control this process:

• Pause Length is the amount of time, measured in multiples of 512 bit times, that the MAC

requests the link partner to halt transmission for.

• Pause Threshold is the amount of time, measured in multiples of 512 bit times, prior to the

expiration of the Pause Length that the MAC transmits another Pause frame to maintain the

link partner in the pause state.

The transmitted Pause Length in the IXF1104 is set by the “FC TX Timer Value ($ Port_Index +

0x07)” on page 163.

The IXF1104 PAUSE frame transmission interval is set by the “Pause Threshold ($ Port_Index +

0x0E)” on page 165.

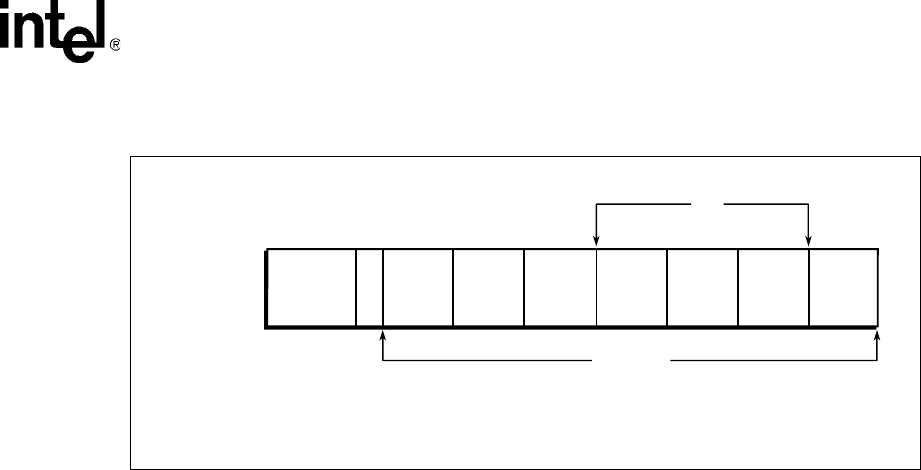

Figure 9. PAUSE Frame Format

B3218-01

DA* or

01-80-

C2-00-

00-01

SA 88-08 FCS

S

F

D

Preamble

61 4662

Pause

Opcode

(00-01)

Pause

Length

22

46

Pad

(with 0s)

42

64 Bytes

Number of bytes

Note: In the Intel

®

IXF1104 architecture, the TX block of the MAC sets this as the pause multicast address.

The RX interface of the MAC will process this as the pause multicast or the MAC address.