IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 211

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

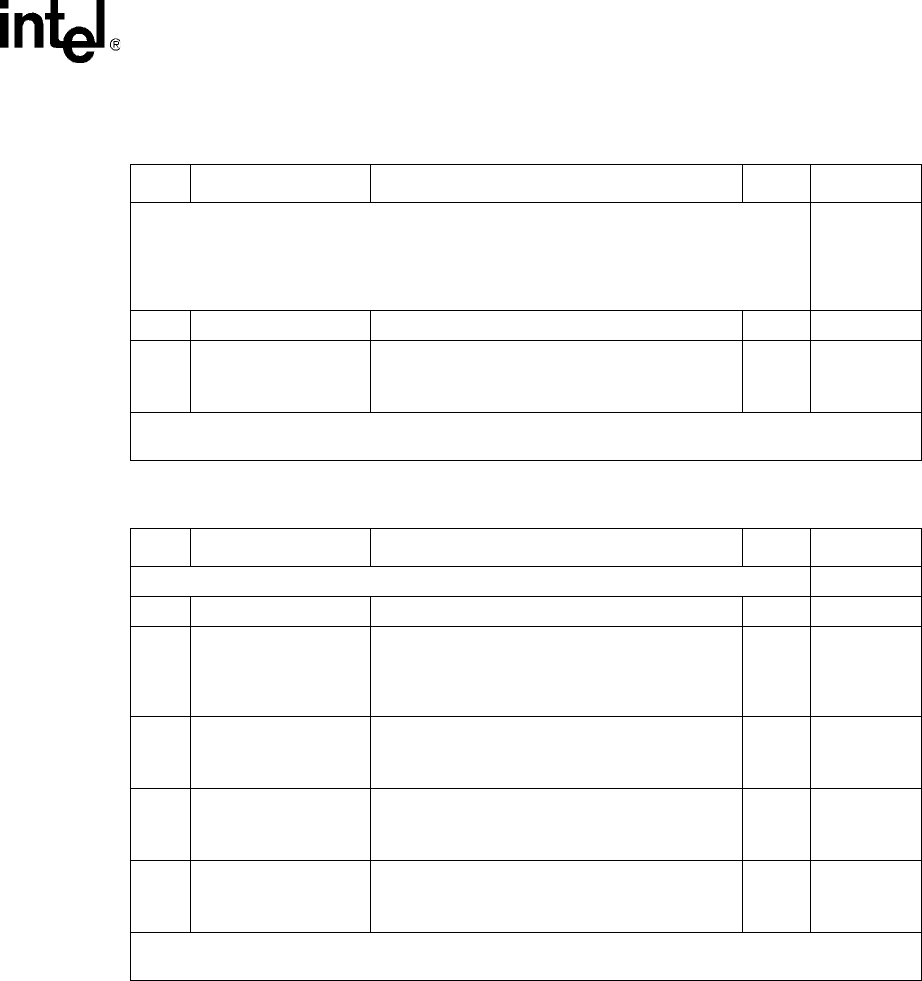

Table 144. Autoscan PHY Address Enable ($0x682)

Bit Name Description Type

1

Default

Register Description:

Defines valid PHY addresses. Each bit enables the corresponding

PHY address.

0 = Disable the PHY address

1 = Enable the PHY address

NOTE: Autoscan is only applicable for the ports in copper mode.

0x00000000

31:4 Reserved Reserved RO 0x0000000

3:0

Autoscan PHY

Address

Autoscan PHY address enable

0 = Disable address

1 = Enable address

R/W 1111

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 145. MDIO Control ($0x683)

Bit Name Description Type

1

Default

Register Description:

Miscellaneous control bits. 0x00000000

31:4 Reserved Reserved RO 0x000

3MDIO in Progress

MDIO progress. This bit reflects the status of

MDIO transaction

0 = MDIO Single command not in progress

1 = MDIO Single Command in progress

RO 0

2

MDIO in Progress

Enable

Enables the MDIO in progress bit

0 = Disable MDIO in progress register bit

1 = Enable MDIO in progress register bit

R/W 0

1 Autoscan Enable

Autoscan enable

0 = Disable Autoscan

1 = Enable Autoscan

R/W 0

0 MDC Speed

MDC speed

0 = MDC runs at 2.5 MHz

1 = MDC runs at 18 MHz

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write