IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 171

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

3:2

2

Reserved Write as 1, ignore on Read. R/W 11

1

2

Reserved Write as 0, ignore on Read. R/W 0

0

2

Reserved Write as 1, ignore on Read. R/W 1

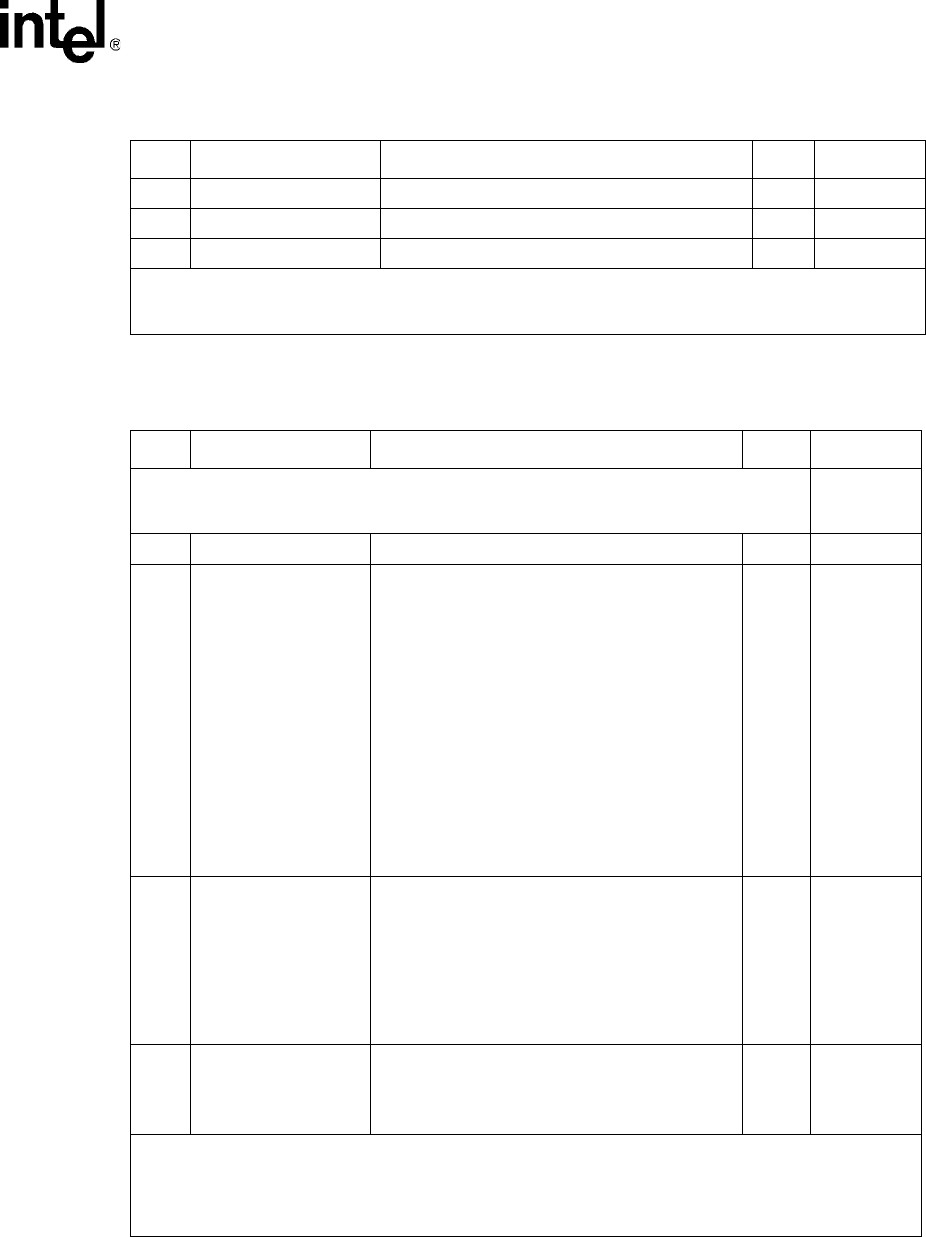

Table 90. Diverse Config Write ($ Port_Index + 0x18) (Sheet 2 of 2)

Bit Name Description Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write

2. Reserved bits must be written to the default value for proper operation.

Table 91. RX Packet Filter Control ($ Port_Index + 0x19) (Sheet 1 of 2)

Bit Name Description Type

1

Default

Register Description:

This register allows for specific packet types to be marked for filtering

and is used in conjunction with the “RX FIFO Errored Frame Drop Counter Ports 0 - 3 ($0x5A2

- 0x5A5)”.

0x00000000

31:6 Reserved Reserved 0

5 CRC Error Pass

This bit enables a Global filter on frames with a

CRC Error.

0 = When CRC Error Pass = 0, all frames with a

CRC Error are marked as bad.

2

1 = Frames with a CRC Error are not marked as

bad and are passed to the SPI3 interface for

transfer as good frames, regardless of the

state of the bits in the “RX FIFO Errored

Frame Drop Enable ($0x59F)”.

NOTE: When the CRC Error Pass Filter bit = 0, it

takes precedence over the other filter bits.

Any packet, whether is a Pause, Unicast,

Multicast or Broadcast packet with a CRC

error, is marked as a bad frame when

CRC Error Pass = 0

R/W 0

4 Pause Frame Pass

This bit enables a Global filter on Pause frames.

0 = All pause frames are dropped.

2

1 = All pause frames are passed to the SPI3

Interface.

NOTE: Pause Frames can only be filtered if

RXFD flow control is enabled in the “FC

Enable ($ Port_Index + 0x12)”.

R/W 0

3 VLAN Drop En

This bit enables a global filter on VLAN frames.

0 = All VLAN frames are passed to the SPI3

Interface.

1 = All VLAN frames are dropped.

2

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

2. Used in conjunction with the “RX FIFO Errored Frame Drop Enable ($0x59F)” on page 195. This allows the

frame to be dropped in the RX FIFO. Otherwise, the frame is sent out the SP3 interface and may be

optionally signaled with an RERR (see bit 0 of “SPI3 Receive Configuration ($0x701)”.