IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet 173

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

8.4.2 MAC RX Statistics Register Overview

The MAC RX Statistics registers contain the MAC receiver statistic counters and are cleared when

read. The software polls these registers and accumulates values to ensure that the counters do not

wrap. The 32-bit counters wrap after approximately 30 seconds.

Table 93 covers the RX statistics for the four MAC ports. Port_Index is the port number (0, 1, 2, or

3).

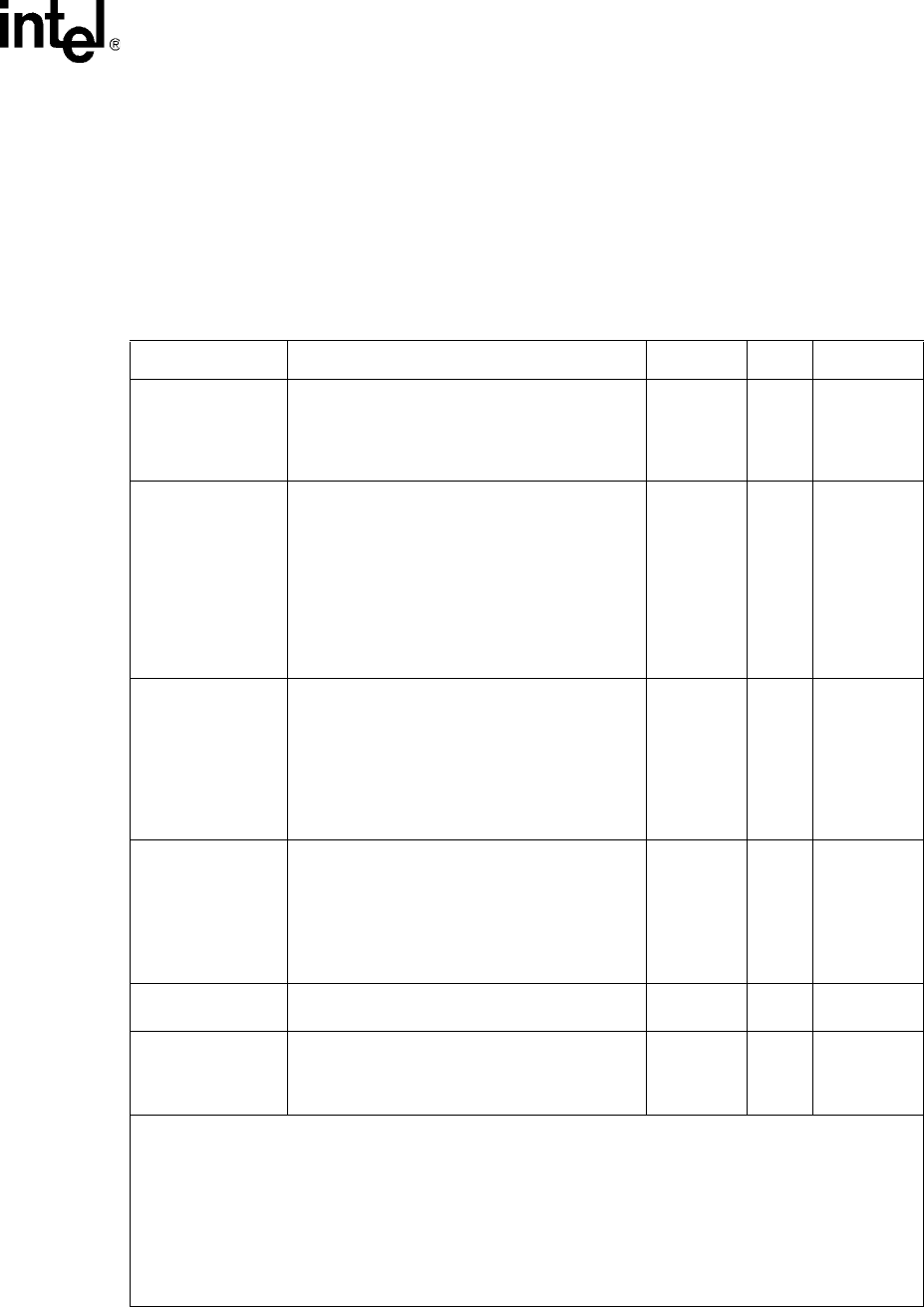

Table 93. MAC RX Statistics ($ Port_Index + 0x20 – + 0x39) (Sheet 1 of 4)

Name Description Address Type

1

Default

RxOctetsTotalOK

Counts the bytes received in all legal frames,

including all bytes from the destination MAC

address to and including the cyclic redundancy

check (CRC). The initial preamble and Start of

Frame Delimiter (SFD) bytes are not counted.

Port_Index

+ 0x20

R 0x00000000

RxOctetsBAD

2

Counts the bytes received in all bad frames with

legal size (frames with CRC error, alignment

errors, or code violations), including all bytes

from the destination MAC address to (and

including) the CRC. The initial preamble and

SFD bytes are not counted. Frames with illegal

size do not add to this counter (shorts, runts,

longs, jabbers, and very longs).

Note: This register does not count octets on

undersized received packets.

Port_Index

+ 0x21

R 0x00000000

RxUCPkts

The total number of unicast packets received

(excluding bad packets).

Note: This count includes non-pause control and

VLAN packets, which are also counted in other

counters. These packet types are counted twice.

Take care when summing register counts for

reporting Management Information Base (MIB)

information.

Port_Index

+ 0x22

R 0x00000000

RxMCPkts

The total number of multicast packets received

(excluding bad packets)

Note: This count includes pause control packets,

which are also counted in the PauseMacControl-

ReceivedCounter. These packet types are

counted twice. Take care when summing register

counts for reporting MIB information.

Port_Index

+ 0x23

R 0x00000000

RxBCPkts

The total number of Broadcast packets received

(excluding bad packets).

Port_Index

+ 0x24

R 0x00000000

RxPkts64Octets

The total number of packets received (including

bad packets) that were 64 octets in length.

Incremented for tagged packets with a length of

64 bytes, including tag field.

Port_Index

+ 0x25

R 0x00000000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write

2. When sending in large frames, the counters can only handle certain limits. The behavior of the LongErrors

and VeryLongErrors counters is as follows: VeryLongErrors counts frames that are 2*maxframesize,

dependent upon where maxframesize is set. If maxframesize sets greater than half of the available count in

RxOctetsBad (2^14-1), VeryLongErrors is never incremented, but LongErrors is incremented. This is due to

a limitation in the counter size, which means that an accurate count will not occur in the RxOctetsBAD

counter if the frame is larger than 2^14-1.

3. This register is relevant only when configured for copper operation.

4. This register is relevant only when configured for fiber operation (line side interface is SerDes).