IXF1104 4-Port Gigabit Ethernet Media Access Controller

168 Datasheet

Document Number: 278757

Revision Number: 007

Revision Date: March 25, 2004

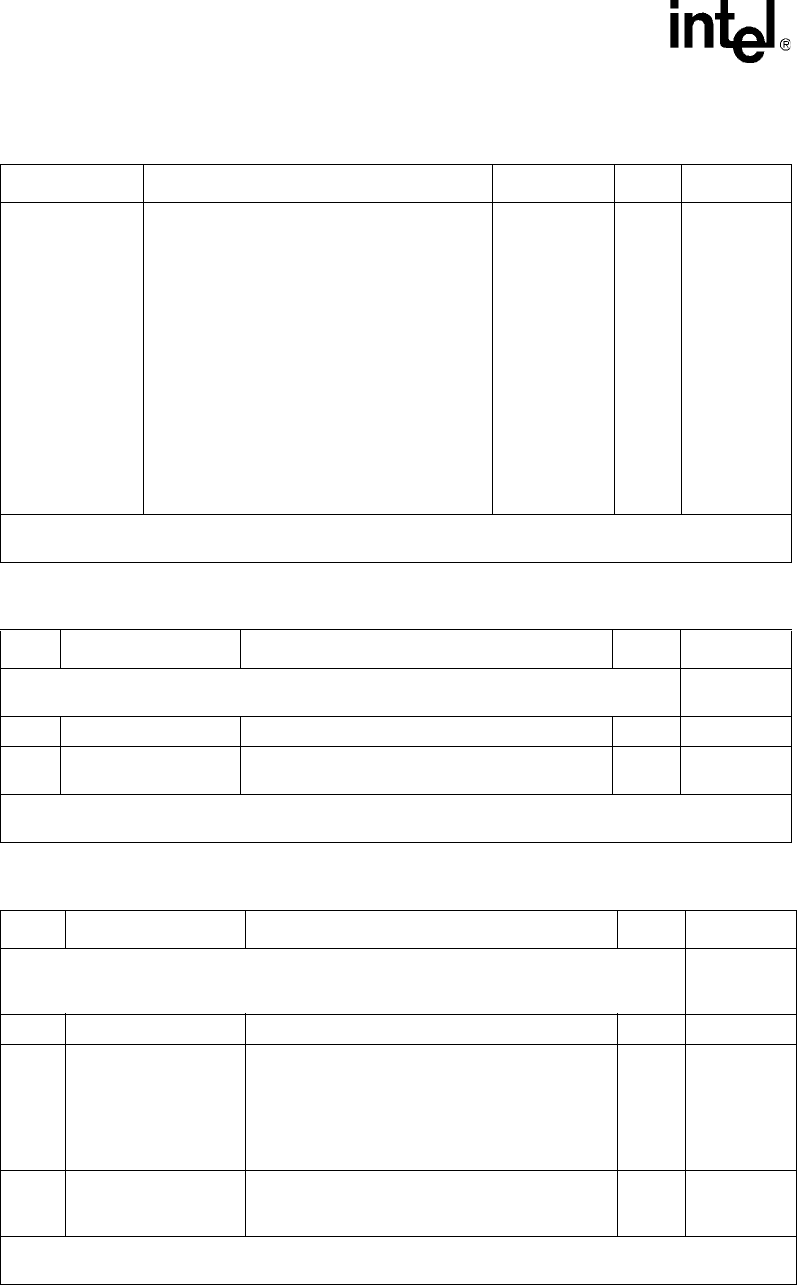

Table 86. Short Runts Threshold ($ Port_Index + 0x14)

Name Description Address Type

1

Default

Short Runts

Threshold

The 5-bit configuration holds the value in bytes,

which applies to the threshold in determining

between runts and short. The bits 4:0 of this

register are alone used.

A received packet is reported as a short packet

when the length (excluding Preamble and

SFD) is less than this value.

A received packet is reported as a runt packet

when the length (excluding Preamble and

SFD) is equal to or greater than this value and

less than 64-bytes.

NOTE: This register is only relevant when the

IXF1104 port is configured for copper

operation (the line side interface is

configured for either RGMII or GMII).

Port_Index +

0x14

R/W 0x00000008

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 87. Discard Unknown Control Frame ($ Port_Index + 0x15)

Bit Name Description Type

1

Default

Register Description:

Discards or forwards unknown control frames. Known control frames

are pause frames.

0x00000000

31:1 Reserved Reserved R 0x00000000

0

Discard Unknown

Control Frame

0 = Forward unknown control frames

1 = Discard unknown control frames

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 88. RX Config Word ($ Port_Index + 0x16) (Sheet 1 of 2)

Bit Name Description Type

1

Default

Register Description:

This register is used in fiber MAC only for auto-negotiation and to report

the receive status. The lower 16 bits of this register are the “config_reg” received from the link

partner, as described in IEEE 802.3 2000 Edition, Section 37.2.1.

0x00000000

31:22 Reserved Reserved RO 0x000

21 An_complete

Auto-negotiation complete. This bit remains

cleared from the time auto-negotiation is reset until

auto-negotiation reaches the “LINK_OK” state. It

remains set until auto-negotiation is disabled or

restarted.

This bit is only valid if auto-negotiation is enabled.

RO 0

20 Rx Sync

0 = Loss of synchronization

1 = Bit synchronization. The bit remains Low until

the register is read.

RO 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write