Return to Section TOC Return to Section TOC Return to Section TOC Return to Section TOC

Return to Master TOC Return to Master TOC Return to Master TOC Return to Master TOC

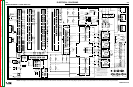

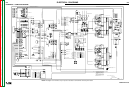

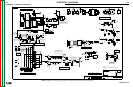

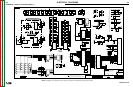

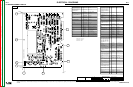

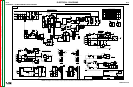

ELECTRICAL DIAGRAMS

G-5

POWER WAVE 450

SCHEMATIC - CONTROL PC BOARD #2

4.75K

R342

4.75K

R344

4.75K

R343

4.75K

R341

4.75K

R339

4.75K

R345

4.75K

R337

28

14

CY7C199

VCC

A0

A9

A4

A8

A12

A14

A10

I/O 3

A13

I/O 1

/WE

A6

I/O 4

A1

GND

A7

I/O 2

I/O 6

I/O 5

I/O 0

A11

/OE

/CE

A3

A5

A2

I/O 7

X46

15

3

4

6

17

22

7

16

18

9

2

10

8

23

24

19

13

26

21

25

11

5

20

1

27

12

ADDR[2]

ADDR[1]

ADDR[8]

ADDR[3]

ADDR[1]

ADDR[7]

ADDR[0]

ADDR[9]

/WE

ADDR[0:11]

ADDR[10]

ADDR[3]

ADDR[6]

ADDR[2]

ADDR[5]

ADDR[4]

/REN

RAM_SEL

D

D

ADDR[6]

ADDR[5]

ADDR[4]

/REN

RAM_SEL

/WE

ADDR[7]

ADDR[9]

ADDR[8]

ADDR[10]

(DSP1 ADDRESS BUS)

G

2241-2

3C: STATIC RAM

4.75K

R338

50V

0.1

C156

475

R47

J24

8

J24

14

J24

10

J24

12

J24

9

J24

11

1W

5.1V

DZ16

J24

6

1W

5.1V

DZ10

475

R43

NOISE_GROUND

+5V

NOISE_GROUND

NOISE_GROUND

NOISE_GROUND

NOISE_GROUND

NOISE_GROUND

475

R42

NOISE_GROUND

NOISE_GROUND

NOISE_GROUND

+15V

J24

3

475

R55

475

R52

J24

2

475

R49

475

R51

1W

5.1V

DZ14

475

R54

1W

5.1V

DZ13

J24

7

475

R50

J24

1

475

R44

1W

5.1V

DZ11

J24

13

J24

5

475

R48

475

R53

475

R56

1W

5.1V

DZ12

1W

5.1V

DZ15

1W

5.1V

DZ17

475

R57

J24

4

475

R45

475

R46

O/D(5)

(DSP2 DATA BUS)

20

10

D2O2

/OE

D0

O6

D1

O7 D7

74AC573

D6

O4

O5

D3

D4

GND

O0

Vcc

O3

O1

D5

LE

X29

5

6

19

18

16

14

9

15

11

12

4

7

1

13

8

2

17

3

O/D(4)

O/D(1)

O/D(12)

20

10

D2O2

/OE

D0

O6

D1

O7 D7

74AC573

D6

O4

O5

D3

D4

GND

O0

Vcc

O3

O1

D5

LE

X30

5

6

19

18

16

14

9

15

11

12

4

7

1

13

8

2

17

3

O/D(11)

O/D(3)

O/D(0)

O/D(2)

O/D(0)

O/D(1)

O/D(2)

O/D(3)

O/D(6)

O/D(13)

O/D(14)

O/D(15)

O/D(11)

O/D(7)

O/D(8)

6B: PARALLEL COMMUNICATION

20

10

D2 O2

/OE

D0

O6

D1

O7D7

74AC573

D6

O4

O5

D3

D4

GND

O0

Vcc

O3

O1

D5

LE

X27

5

6

19

18

16

14

9

15

11

12

4

7

1

13

8

2

17

3

O/D(8)

O/D(15)

O/D(12)

O/D(4)

O/D(7)

O/D(13)

READ_0

O/D(9)

O/D(10)

O/D(8)

O/D(14)

O/D(15)

O/D(13)

O/D(12)

DSP2_W2

O/D(9)

O/D(10)O/D(10)

O/D(9)

O/D(5)

O/D(6)

O/D(0:15)

D

CLK

WRITE_0

RD_DSP2

WRITE_0

RD_DSP2

O/D(11)

O/D(14)

O/D(6)

O/D(5)

O/D(7)

O/D(1)

O/D(2)

O/D(3)

O/D(4)

O/D(0)

DSP2_W2

D

O/D(0:15)

READ_0

J22

8

SCALE

D

CLEVELAND, OHIO U.S.A.

J22

7

50V

0.1

C32

1.00K

R64

1.00K

R180

Q5

2N4401

10K

R65

1.00K

R173

X41

11

13

12

50V

820p

C53

1N4936

D51

1.00K

R67

4.75K

R68

X21

13

12

20

10

PAL16R4

OE

I1

D0

O1

CLK

O0

D1

D2

D3

O2

O3

Vcc

GND

17

I5

I3

I4

I0

I2

16

X39

5

6

19

18

16

14

9

15

11

12

4

7

1

13

8

2

17

3

A

OUTPUT_ON

CLR_CAP

Q4

2N4401

ON HOLES SIZES PER E-2056

11-25-92

ON 2 PLACE DECIMALS IS + .O2

CHK.

J22

2

X21

11

10

STROBE_AD

D

+15V

D

CLK

A

+15V

FAULT

OVR_CUR

DSP / FUNCTION GENERATOR - SHEET 2

NOT SHOW THE EXACT COMPONENTS OR CIRCUITRY OF CONTROLS HAVING A COMMON CODE

N.A. SINCE COMPONENTS OR CIRCUITRY ON A PRINTED CIRCUIT BOARD MAY CHANGE

WITHOUT AFFECTING THE INTERCHANGEABILITY OF A COMPLETE BOARD, THIS DIAGRAM MAY

VOLTAGE NET

DR.

DATE

WITH PUBLISHED STANDARDS

NO.

2241-2

COMMON CONNECTION

EARTH GROUND CONNECTION

POWER SUPPLY SOURCE POINT

G

SHT.

POWER WAVE

SUBJECT

CONTROL SCHEMATIC

TYPE

SUP’S’D’G.

ON 3 PLACE DECIMALS IS + .OO2

3D: ANALOG/DIGITAL CONVERTERS

50V

0.1

C60

A/D CONVERSION

74AC04

X21

14

7

X41

NAND

SCHMITT

14

7

50V

0.1

C61

(DSP2 MISC. I/O BUS)

ADC1061

Vin

DVcc

Vref+

Vref-

DB9

S/H

DB6

DB7

RD

DB8

DB5

DB4

DB3

DB2

DB1

DB0

GND

CS

INT

AVcc

X14

6

1

19

18

16

14

5

15

11

12

9

2

4

13

7

8

17

3

20

10

50V

0.1

C59

1.0

35V

C130

50V

0.1

C62

TMS320E14

X25

34

3

AD_DATA[0]

+5V

D

AD_DATA[0:15]

AD_DATA[2]

AD_DATA[1]

D

AD_DATA[9]

AD_DATA[8]

AD_DATA[7]

AD_DATA[3]

AD_DATA[6]

AD_DATA[5]

AD_DATA[4]

AD_DATA[0]

A/D CONVERSION

PAL16R4

X39

10

20

CLK

DATA[11]

DATA[12]

DATA[10]

DATA[9]

DATA[10]

DATA[6]

DATA[4]

DATA[8]

DATA[13]

DATA[11]

DATA[13]

DATA[12]

DATA[15]DATA[15]

DATA[14]

DATA[5]

DATA[3]

DATA[1]

DATA[2]

DATA[0]DATA[0]

DATA[7]

DATA[1]

DATA[5]

DATA[2]

DATA[3]

DATA[8]

DATA[7]

DATA[14]

DATA[6]

DATA[12]

DATA[8]

DATA[10]

DATA[9]

DATA[11]

DATA[15]

DATA[4]

DATA[13]

DATA[14]

DATA[9]

DATA[0:15]

OUTPUT_ON

RAM_SEL

STROBE_AD

DATA[2]

DATA[3]

DATA[4]

DATA[1]

DATA[0]

DATA[6]

DATA[5]

DATA[7]

(3)

10K

R61

AD_DATA[1]

50V

0.1

C41

10K

R264

DSP_A0

DSP_A2

STROBE_AD

V_AD

10.0K

R268

50V

0.1

C37

18

15V

C38

18

15V

C39

A D

RD_VOL

AD_DATA[3]

AD_DATA[4]

AD_DATA[5]

AD_DATA[6]

AD_DATA[9]

AD_DATA[7]

AD_DATA[8]

AD_DATA[2]

20

10

D2 O2

/OE

D0

O6

D1

O7D7

74AC573

D6

O4

O5

D3

D4

GND

O0

Vcc

O3

O1

D5

LE

X28

5

6

19

18

16

14

9

15

11

12

4

7

1

13

8

2

17

3

100K

R263

ADC1061

INT

AVcc

RD

CS

DB9

S/H

DB6

DB7

DVcc

DB8

DB5

DB4

DB3

DB2

DB1

DB0

GND

Vref-

Vref+

Vin

X37

8

6

19

18

16

14

7

15

11

12

4

9

1

13

5

2

17

3

20

10

VOLTAGE

10.0K

R267

50V

0.1

C40

+Vref_V

+5V

50V

0.1

C67

74AC139

X43

16

8

18

15V

C35

50V

0.1

C69

DATA[5]

1.0

35V

C70

50V

0.1

C68

50V

0.1

C66

DATA[6]

74AC153

X44

16

8

DATA[7]

DATA[1]

DATA[2]

DATA[0:15]

RD_CUR

A

I_AD

+5V

+Vref_I

STROBE_AD

DATA[10]

DATA[8]

DATA[9]

DATA[3]

DATA[0]

DATA[4]

DATA[11]

DATA[15]

DATA[14]

DATA[13]

DATA[12]

(DSP1 DATA BUS)

CURRENT

18

15V

C33

50V

0.1

C34

TMS320E14

X38

34

3

ADDR[0]

10K

R62

D

10K

R58

10K

R60

D

100V

330p

C56

10K

R63

10K

R59

10K

R262

/WE

ADDR[1]

ADDR[0:11]

ADDR[5]

ADDR[7]

ADDR[8]

ADDR[4]

ADDR[3]

ADDR[9]

ADDR[2]

ADDR[10]

ADDR[6]

/REN

/WTD

RESET

+5V

ADDR[0]

DSP_A11

LATCH_READ

DIRECTION

RD_HIGH

RD_LOW

+5V

D

3B: DSP 1 FUNCTION GENERATOR

DSP 1

(3)

(3)

(3)

33

4

34

3

TCLK2/CLKX

IOP13

CMP1

CMP2

CAP0

IOP3

IOP2

IOP1

IOP8

IOP6

IOP9

IOP7

IOP5

CAP1

CMP4/CAP2/FSX

IOP4

A10

IOP0

A0

A8

NMI/MC/MP

A7

/WTD

/RS

A6

A5

A4

A3

IOP10

A2

CLKOUT

A9

CMP5/CAP3/FSX

IOP11

/INT

/REN

/WE

CMP3

A1

RXD

D0

D1

D14

D11

D10

D9

CLKIN

D8

TXD

D15

D6

D3

D4

TCLK1/CLKR

D12

D13

D2

CMP0

IOP12

IOP15

IOP14

D5

D7

TMS320E14

Vcc1

Vcc2

Vss1

Vss2

A11

X38

62

64

63

39

36

43

46

49

24

40

19

47

1

59

50

61

60

57

58

35

7

11

10

48

8

65

31

32

30

29

12

9

6

14

13

21

20

2825

26

27

5

23

22

67

66

15

17

53

16

18

37

56

54

55

52

51

45

44

41

38

42

68

2

28

14

CY7C199

VCC

A0

A9

A4

A8

A12

A14

A10

I/O 3

A13

I/O 1

/WE

A6

I/O 4

A1

GND

A7

I/O 2

I/O 6

I/O 5

I/O 0

A11

/OE

/CE

A3

A5

A2

I/O 7

X45

15

3

4

6

17

22

7

16

18

9

2

10

8

23

24

19

13

26

21

25

11

5

20

1

27

12

OUT

GND

Vcc

X24

25mhz

50V

0.1

C48

50V

0.1

C63

50V

0.1

C44

(PSD301)

8

16

A1b

Y0b

74AC139

A1a

select b

select a

Y0a

VCC

Y2a

GND

Y3a

Y1b

Y1a

Y3b

A0a

A0b

Y2b

X43

7

13

3

14

1

15

2

4

5

12

11

9

10

6

X21

1

2

1.0

35V

C47

X21

3

4

50V

0.1

C64

X45

CY7C199

28

14

X46

CY7C199

28

14

50V

0.1

C65

74AC573

X28

20

10

74AC573

X27

20

10

74AC573

X29

20

10

74AC139

X42

16

8

50V

0.1

C43

74AC573

X30

20

10

50V

0.1

C155

50V

0.1

C42

OE_LOW

CLK

D

DSP2_W2

DSP2_W0

RD_DSP2

+5V

+5V

DSP_A2

DSP_REN

DSP_A0

DSP_WE

(3)

3A: BUS DECODE DSP 2

10K

R74

DIRECTION

Q7

2N4401

10K

R72

X21

5

6

RD_HIGH

RD_LATCH

ADDR[0]

D

WRITE_1

WRITE_0

READ_0

ADDR[0:11]

DSP_A11

/REN

/WE

ADDR[0:11]

OE_HIGH

RD_LOW

RD_LATCH

RD_LATCH

3B: BUS DECODE DSP 1

*

DIRECTION LOW......DSP 1 -> HC11

DIRECTION HIGH.....HC11 -> DSP 1

FET BANK A

6A: CONTROL DATA FLOW (DSP 1 <> HC11)

1.00K

R179

J22

1

Q6

2N4401

4.75K

R70

50V

0.1

C31

1.00K

R71

1.00K

R73

1N4936

D50

1.00K

R69

50V

820p

C52

8

16

A1b

Y0b

74AC139

A1a

select b

select a

Y2a

VCC

Y0a

GND

Y3a

Y1b

Y1a

Y2b

A0a

A0b

Y3b

X42

7

13

3

14

1

15

2

6

5

12

11

10

9

4

X41

6

5

4

X41

3

2

1

100V

330p

C30

OUTPUT_ON

RD_VOL

DSP_REN

D

100K

R266

33

4

34

3

TXD

CMP2

/RS

/WTD

CAP1

D3

D2

D1

CLKOUT

D6

TCLK2/CLKX

D7

D5

D15

D14

D4

A10

D0

A0

A8

D13

A7

D12

D11

A6

A5

A4

A3

TCLK1/CLKR

A2

IOP11

A9

X25

CLKIN

D8

D9

D10

IOP8

A1

IOP0

IOP1

/INT

/REN

IOP15

IOP13

IOP10

IOP12

IOP9

NMI/MC/MP

IOP6

IOP3

IOP4

RXD

IOP14

/WE

IOP2

A11

CMP3

CMP0

CMP1

IOP5

IOP7

TMS320E14

Vcc1

Vcc2

Vss1

Vss2

54

56

55

15

18

16

29

31

38

30

37

41

42

51

32

53

52

44

45

22

17

47 48

68

66

65

2

1

7

8

12

9

6

14

13

21

20

2825

26

27

5

40

39

35

36

46

43

61

49

50

24

64

62

63

60

59

58

57

11

10

19

67

23

NUMBER.

AD_DATA[4]

AD_DATA[1]

AD_DATA[2]

AD_DATA[8]

AD_DATA[0]

AD_DATA[5]

AD_DATA[6]

AD_DATA[7]

AD_DATA[9]

AD_DATA[0:15]

AD_DATA[3]

CLR_CAP

RD_CUR

D

DSP_WE

+5V

STROBE_AD

/XIRQ

CLR_SHUNT

/WTD

D

RESET

CAP1

NOTES :

3Eb: WATCH DOG

CMP5/CAP3/FSX

CAP0

3A: DSP 2

CMP4/CAP2/FSR

(2)

10K

R41

FILE: G2241_2A1

FRAME CONNECTION

SUPPLY

DIODES =

(UNLESS OTHERWISE SPECIFIED)

1A, 400V

JRF

THE LINCOLN ELECTRIC CO.

34

5: PAL

UNLESS OTHERWISE SPECIFIED)

52

RESISTORS = Ohms (

93

1/4W

GENERAL INFORMATION

35

UNLESS OTHERWISE SPECIFIED)

Q-

ELECTRICAL SYMBOLS PER E1537

CAPACITORS =

.022/50V

MFD

(

156

DZ-

X-

* INDICATES CHANGE FROM "XRF" VERSION

345

*

FET BANK B

(FROM HC11)

CHB

(4)

2O: MAIN FET DRIVE

LAST NO. USED

LABELS

C-

R-

D-

(DSP1 ADDRESS BUS)

CHA

(PSD301)

(DSP1, PORT1)

(DSP1, PORT1)

EQUIP.

MATERIAL TOLERANCE ("t") TO AGREE

ON ALL ANGLES IS + .5 OF A DEGREE

Ch’ge.Sht.No.

UNLESS OTHERWISE SPECIFIED TOLERANCE

NONE

8

16

I0a

74AC153

/Ea

Zb

I1b

GND

Vcc

I3b

I0b

S1

I2a

I2b

I1a

I3a

/Eb

Za

S0

X44

4

2

13

1

15

7

11

6

3

9

10

5

14

12

1-6-98B

8-11-95C

1-30-98B

8-13-99B

G-5

NOTE: This diagram is for reference only. It may not be accurate for all machines covered by this manual.