107

CHAPTER 5 CPU ARCHITECTURE

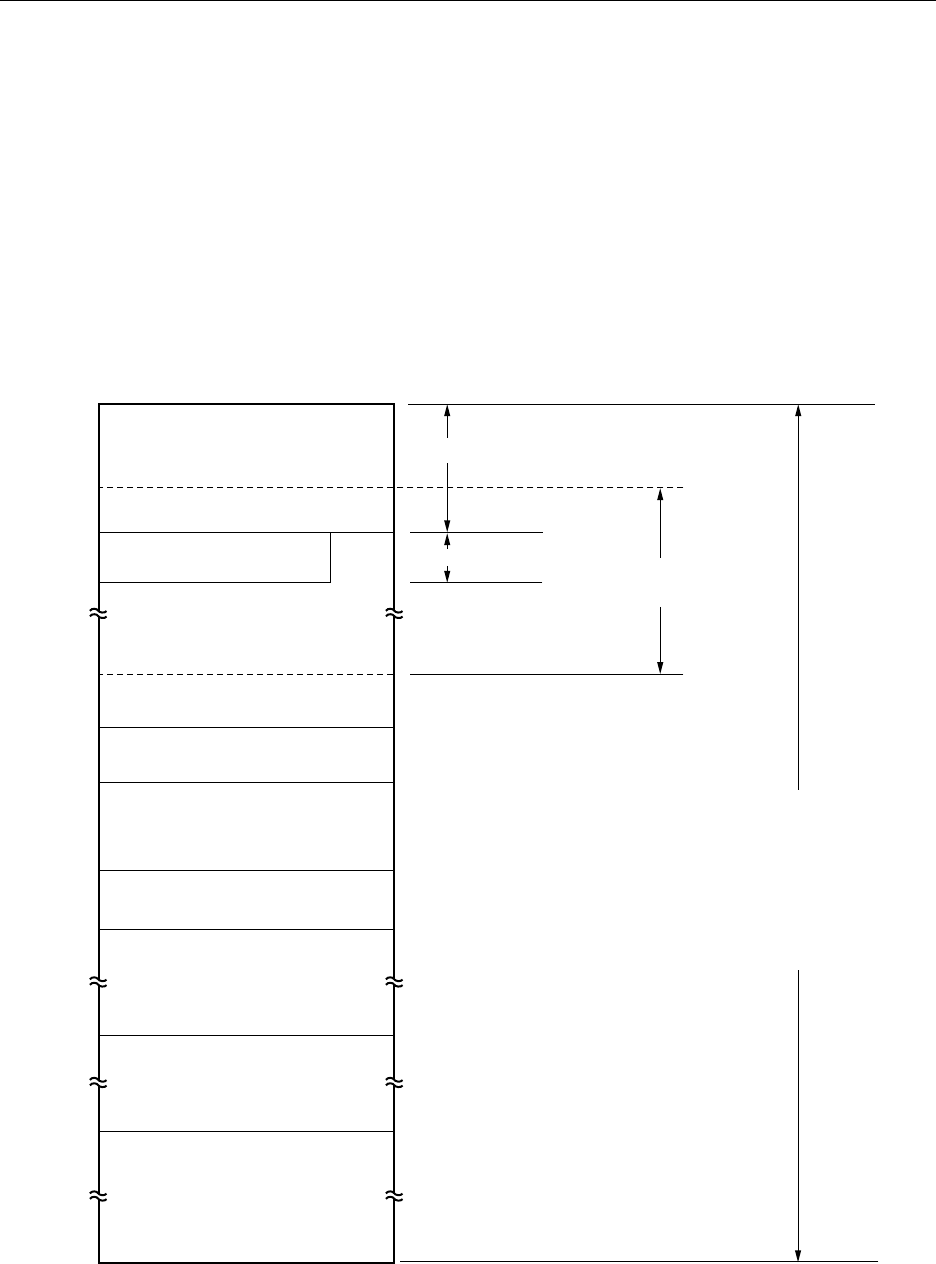

0000H

General Registers

32 x 8 bits

Internal ROM

49152 x 8 bits

Internal Buffer RAM

32 x 8 bits

External Memory

13312 x 8 bits

Reserved

C000H

BFFFH

F800H

F7FFH

FAC0H

FABFH

FAE0H

FADFH

FEE0H

FEDFH

FF00H

FEFFH

FFFFH

Internal High-speed RAM

1024 x 8 bits

Reserved

FB00H

FAFFH

F400H

F3FFH

FF20H

FF1FH

FE20H

FE1FH

Special Function

Registers (SFRs)

256 x 8 bits

Internal Expansion RAM

1024 x 8 bits

SFR Addressing

Register Addressing

Short Direct

Addressing

Direct Addressing

Register Indirect

Addressing

Based Addressing

Based Indexed

Addressing

5.1.5 Data memory addressing

Addressing is a method to specify the instruction address to be executed next and the register and memory address

to be manipulated when instructions are executed. The instruction address to be executed next is addressed by the

program counter (PC) (for details, refer to 5.3 Instruction Address Addressing).

For the addressing of the memory to be manipulated when instructions are executed, the

µ

PD78078 and 78078Y

Subseries are provided with various addressing modes for optimum addressing. Special addressing methods are

possible to meet the functions of the special function registers (SFRs) and general registers. The data memory space

is the entire 64-Kbyte space (0000H to FFFFH). Figures 5-4 to 5-6 show the data memory addressing modes.

For details of addressing, refer to 5.4 Operand Address Addressing.

Figure 5-4. Data Memory Addressing (

µ

PD78076, 78076Y)