14

3.2.17 AVSS ............................................................................................................................................. 76

3.2.18 RESET ......................................................................................................................................... 76

3.2.19 X1 and X2 .................................................................................................................................... 76

3.2.20 XT1 and XT2 ............................................................................................................................... 76

3.2.21 V

DD ............................................................................................................................................... 77

3.2.22 V

SS ................................................................................................................................................ 77

3.2.23 VPP (

µ

PD78P078 only) ................................................................................................................ 77

3.2.24 IC (Mask ROM version only) ...................................................................................................... 77

3.3 Input/output Circuits and Recommended Connection of Unused Pins ........................ 78

CHAPTER 4 PIN FUNCTION (

µ

PD78078Y SUBSERIES) ................................................................... 83

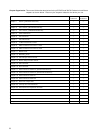

4.1 Pin Function List.................................................................................................................... 83

4.1.1 Normal operating mode pins ...................................................................................................... 83

4.1.2 PROM programming mode pins (

µ

PD78P078Y only) ............................................................... 87

4.2 Description of Pin Functions ............................................................................................... 88

4.2.1 P00 to P07 (Port 0) ..................................................................................................................... 88

4.2.2 P10 to P17 (Port 1) ..................................................................................................................... 88

4.2.3 P20 to P27 (Port 2) ..................................................................................................................... 89

4.2.4 P30 to P37 (Port 3) ..................................................................................................................... 90

4.2.5 P40 to P47 (Port 4) ..................................................................................................................... 90

4.2.6 P50 to P57 (Port 5) ..................................................................................................................... 91

4.2.7 P60 to P67 (Port 6) ..................................................................................................................... 91

4.2.8 P70 to P72 (Port 7) ..................................................................................................................... 92

4.2.9 P80 to P87 (Port 8) ..................................................................................................................... 92

4.2.10 P90 to P96 (Port 9) ..................................................................................................................... 93

4.2.11 P100 to P103 (Port 10) ............................................................................................................... 93

4.2.12 P120 to P127 (Port 12) ............................................................................................................... 93

4.2.13 P130 and P131 (Port 13) ............................................................................................................ 94

4.2.14 AV

REF0 .......................................................................................................................................... 94

4.2.15 AV

REF1 .......................................................................................................................................... 94

4.2.16 AVDD ............................................................................................................................................. 94

4.2.17 AVSS ............................................................................................................................................. 94

4.2.18 RESET ......................................................................................................................................... 94

4.2.19 X1 and X2 .................................................................................................................................... 94

4.2.20 XT1 and XT2 ............................................................................................................................... 94

4.2.21 V

DD ............................................................................................................................................... 95

4.2.22 VSS ................................................................................................................................................ 95

4.2.23 VPP (

µ

PD78P078Y only).............................................................................................................. 95

4.2.24 IC (Mask ROM version only) ...................................................................................................... 95

4.3 Input/output Circuits and Recommended Connection of Unused Pins ........................ 96

CHAPTER 5 CPU ARCHITECTURE .................................................................................................... 101

5.1 Memory Spaces.................................................................................................................... 101

5.1.1 Internal program memory space .............................................................................................. 104

5.1.2 Internal data memory space ..................................................................................................... 106

5.1.3 Special function register (SFR) area ........................................................................................ 106

5.1.4 External memory space ............................................................................................................ 106

5.1.5 Data memory addressing .......................................................................................................... 107