588

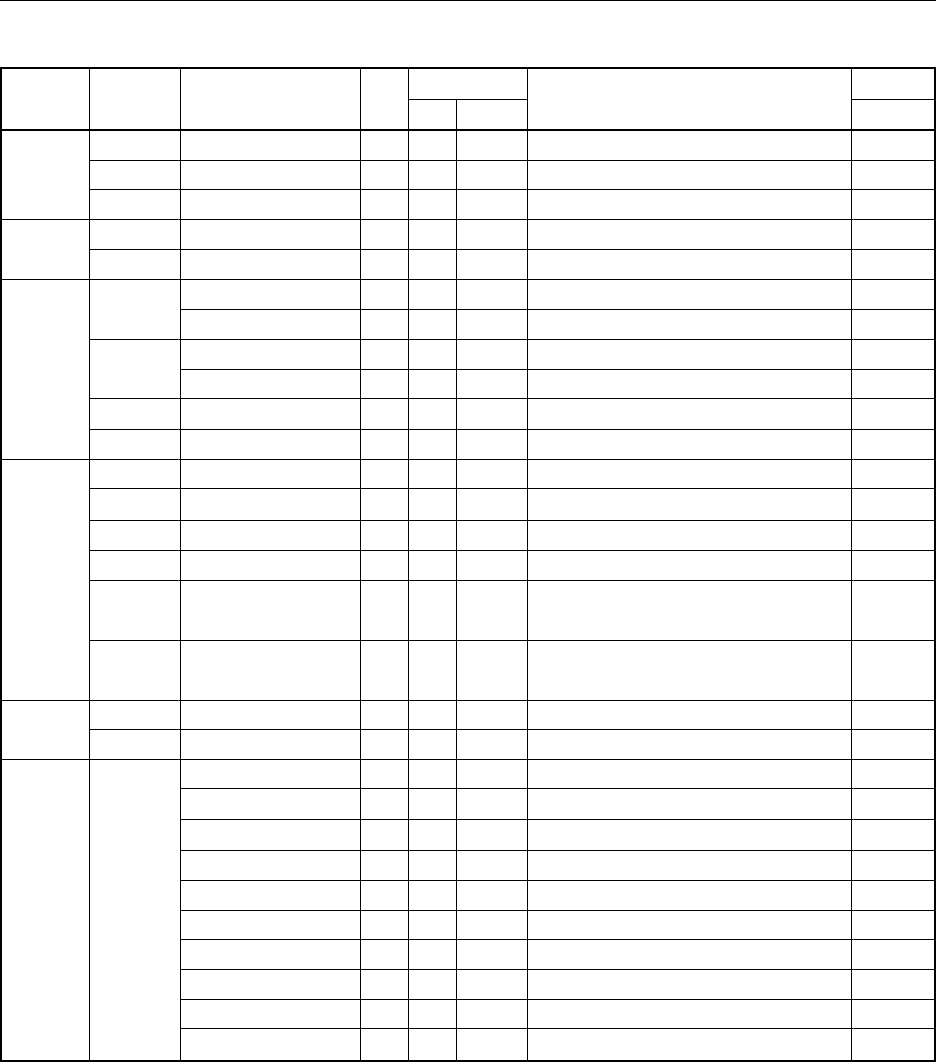

CHAPTER 28 INSTRUCTION SET

Instruction Mnemonic Operands Byte Clock Operation Flag

Group

Note 1 Note 2

ZACCY

16-bit ADDW AX, #word 3 6 — AX, CY ← AX + word x x x

operation SUBW AX, #word 3 6 — AX, CY ← AX – word x x x

CMPW AX, #word 3 6 — AX – word x x x

Multiply MULU X 2 16 — AX ← A x X

divide DIVUW C 2 25 — AX (Quotient), C (Remainder) ← AX/C

Increment INC r 1 2 — r ← r + 1 x x

decrement saddr 2 4 6 (saddr) ← (saddr) + 1 x x

DEC r 1 2 — r ← r – 1 x x

saddr 2 4 6 (saddr) ← (saddr) – 1 x x

INCW rp 1 4 — rp ← rp + 1

DECW rp 1 4 — rp ← rp – 1

Rotate ROR A, 1 1 2 — (CY, A7 ← A0, Am - 1 ← Am) x 1 time x

ROL A, 1 1 2 — (CY, A0 ← A7, Am + 1 ← Am) x 1 time x

RORC A, 1 1 2 — (CY ← A0, A7 ← CY, Am - 1 ← Am) x 1 time x

ROLC A, 1 1 2 — (CY ← A7, A0 ← CY, Am + 1 ← Am) x 1 time x

ROR4 [HL] 2 10 12+n+m A3 - 0 ← (HL)3 - 0, (HL)7 - 4 ← A3 - 0,

(HL)3 - 0 ← (HL)7 - 4

ROL4 [HL] 2 10 12+n+m A3 - 0 ← (HL)7 - 4, (HL)3 - 0 ← A3 - 0,

(HL)7 - 4 ← (HL)3 - 0

BCD ADJBA 2 4 — Decimal Adjust Accumulator after Addition x x x

adjust ADJBS 2 4 — Decimal Adjust Accumulator after Subtract x x x

Bit mani- MOV1 CY, saddr.bit 3 6 7 CY ← (saddr.bit) x

pulation CY, sfr.bit 3 — 7 CY ← sfr.bit x

CY, A.bit 2 4 — CY ← A.bit x

CY, PSW.bit 3 — 7 CY ← PSW.bit x

CY, [HL].bit 2 6 7 + n CY ← (HL).bit x

saddr.bit, CY 3 6 8 (saddr.bit) ← CY

sfr.bit, CY 3 — 8 sfr.bit ← CY

A.bit, CY 2 4 — A.bit ← CY

PSW.bit, CY 3 — 8 PSW.bit ← CY x x

[HL].bit, CY 2 6 8+n+m (HL).bit ← CY

Notes 1. For instructions that access the internal high-speed RAM area or perform no data access

2. For instructions that access an area other than the internal high-speed RAM area

Remarks 1. One clock in the “Clock” columns is equal to one cycle of the CPU clock (f

CPU) selected by the processor

clock control register (PCC).

2. The values in the “Clock” column assumes that the internal ROM area contains programs.

3. n indicates wait cycles to be inserted when an external expansion memory area is read from.

4. m indicates wait cycles to be inserted when an external expansion memory area is written to.