388

CHAPTER 18 SERIAL INTERFACE CHANNEL 0 (

µ

PD78078Y Subseries)

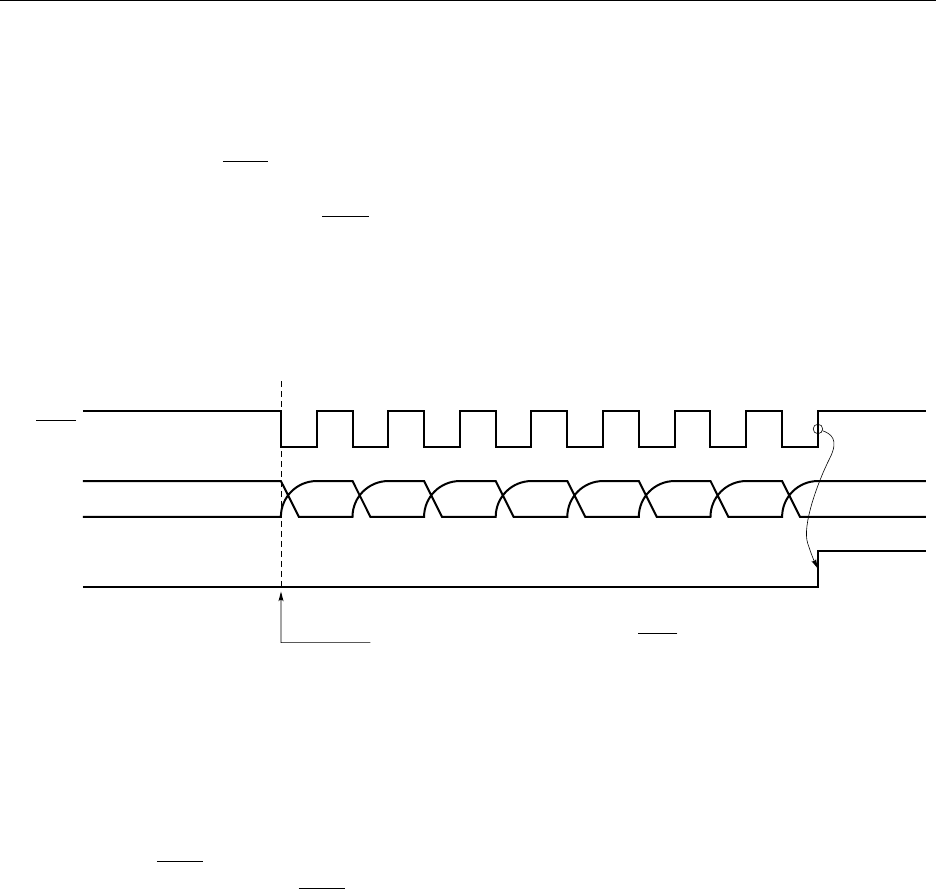

(2) Communication operation

The 2-wire serial I/O mode is used for data transmission/reception in 8-bit units. Data transmission/reception

is carried out bit-wise in synchronization with the serial clock.

Shift operation of the serial I/O shift register 0 (SIO0) is carried out in synchronization with the falling edge

of the serial clock (SCK0). The transmit data is held in the SO0 latch and is output from the SB0/SDA0/

P25 (or SB1/SDA1/P26) pin on an MSB-first basis. The receive data input from the SB0 (or SB1) pin is latched

into SIO0 at the rising edge of SCK0.

Upon termination of 8-bit transfer, the SIO0 operation stops automatically and the interrupt request flag

(CSIIF0) is set.

Figure 18-11. 2-Wire Serial I/O Mode Timings

The SB0 (or SB1) pin specified for the serial data bus is an N-ch open-drain input/output and thus it must

be externally connected to a pull-up resistor. Because it is necessary to set N-ch open-drain output to high-

impedance state for data reception, write FFH to SIO0 in advance.

The SB0 (or SB1) pin generates the SO0 latch status and thus the SB0 (or SB1) pin output status can be

manipulated by setting the bit 0 (RELT) and bit 1 (CMDT) of the serial bus interface control register (SBIC).

However, do not carry out this manipulation during serial transfer.

Control the SCK0 pin output level in the output mode (internal system clock mode) by manipulating the P27

output latch (refer to 18.4.7 SCK0/SCL/P27 pin output manipulation).

1234 5 6 7 8

SCK0

D7 D6 D5 D4 D3 D2 D1 D0

SB0 (SB1)

CSIIF0

Transfer Start at the Falling Edge of SCK0

End of Transfer