591

CHAPTER 28 INSTRUCTION SET

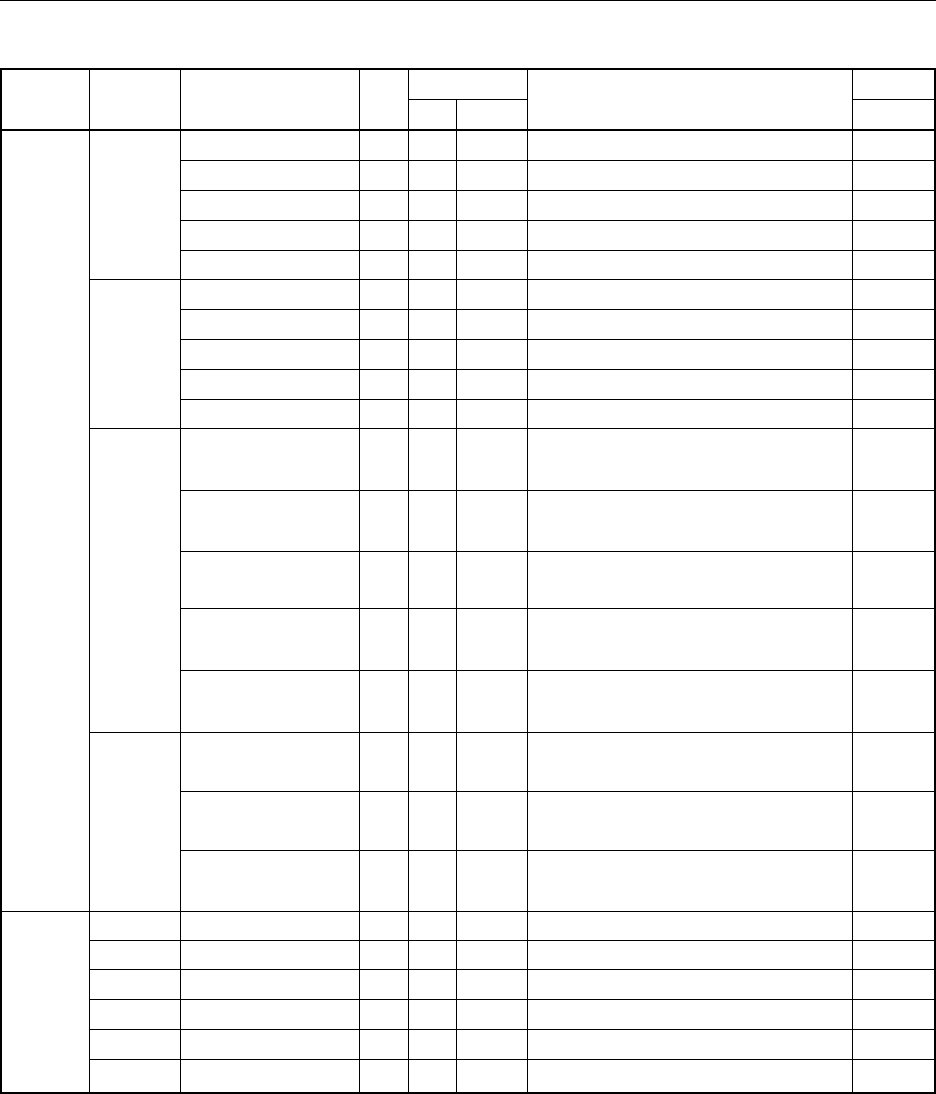

Instruction Mnemonic Operands Byte Clock Operation Flag

Group

Note 1 Note 2

ZACCY

Conditional

BT saddr.bit, $addr16 3 8 9 PC ← PC + 3 + jdisp8 if(saddr.bit) = 1

branch sfr.bit, $addr16 4 — 11 PC ← PC + 4 + jdisp8 if sfr.bit = 1

A.bit, $addr16 3 8 — PC ← PC + 3 + jdisp8 if A.bit = 1

PSW.bit, $addr16 3 — 9 PC ← PC + 3 + jdisp8 if PSW.bit = 1

[HL].bit, $addr16 3 10 11 + n PC ← PC + 3 + jdisp8 if (HL).bit = 1

BF saddr.bit, $addr16 4 10 11 PC ← PC + 4 + jdisp8 if(saddr.bit) = 0

sfr.bit, $addr16 4 — 11 PC ← PC + 4 + jdisp8 if sfr.bit = 0

A.bit, $addr16 3 8 — PC ← PC + 3 + jdisp8 if A.bit = 0

PSW.bit, $addr16 4 — 11 PC ← PC + 4 + jdisp8 if PSW. bit = 0

[HL].bit, $addr16 3 10 11 + n PC ← PC + 3 + jdisp8 if (HL).bit = 0

BTCLR saddr.bit, $addr16 4 10 12 PC ← PC + 4 + jdisp8 if(saddr.bit) = 1

then reset(saddr.bit)

sfr.bit, $addr16 4 — 12 PC ← PC + 4 + jdisp8 if sfr.bit = 1

then reset sfr.bit

A.bit, $addr16 3 8 — PC ← PC + 3 + jdisp8 if A.bit = 1

then reset A.bit

PSW.bit, $addr16 4 — 12+n+m PC ← PC + 4 + jdisp8 if PSW.bit = 1 x x x

then reset PSW.bit

[HL].bit, $addr16 3 10 12 PC ← PC + 3 + jdisp8 if (HL).bit = 1

then reset (HL).bit

DBNZ B, $addr16 2 6 — B ← B – 1, then

PC ← PC + 2 + jdisp8 if B ≠ 0

C, $addr16 2 6 — C ← C –1, then

PC ← PC + 2 + jdisp8 if C ≠ 0

saddr. $addr16 3 8 10 (saddr) ← (saddr) – 1, then

PC ← PC + 3 + jdisp8 if(saddr) ≠ 0

CPU SEL RBn 2 4 — RBS1, 0 ← n

control NOP 1 2 — No Operation

EI 2 — 6 IE ← 1 (Enable Interrupt)

DI 2 — 6 IE ← 0 (Disable Interrupt)

HALT 2 6 — Set HALT Mode

STOP 2 6 — Set STOP Mode

Notes 1. For instructions that access the internal high-speed RAM area or perform no data access

2. For instructions that access an area other than the internal high-speed RAM area

Remarks 1. One clock in the “Clock” columns is equal to one cycle of the CPU clock (f

CPU) selected by the processor

clock control register (PCC).

2. The values in the “Clock” column assumes that the internal ROM area contains programs.

3. n indicates wait cycles to be inserted when an external expansion memory area is read from.

4. m indicates wait cycles to be inserted when an external expansion memory area is written to.