6-16 Instruction Set of the I/O Processor

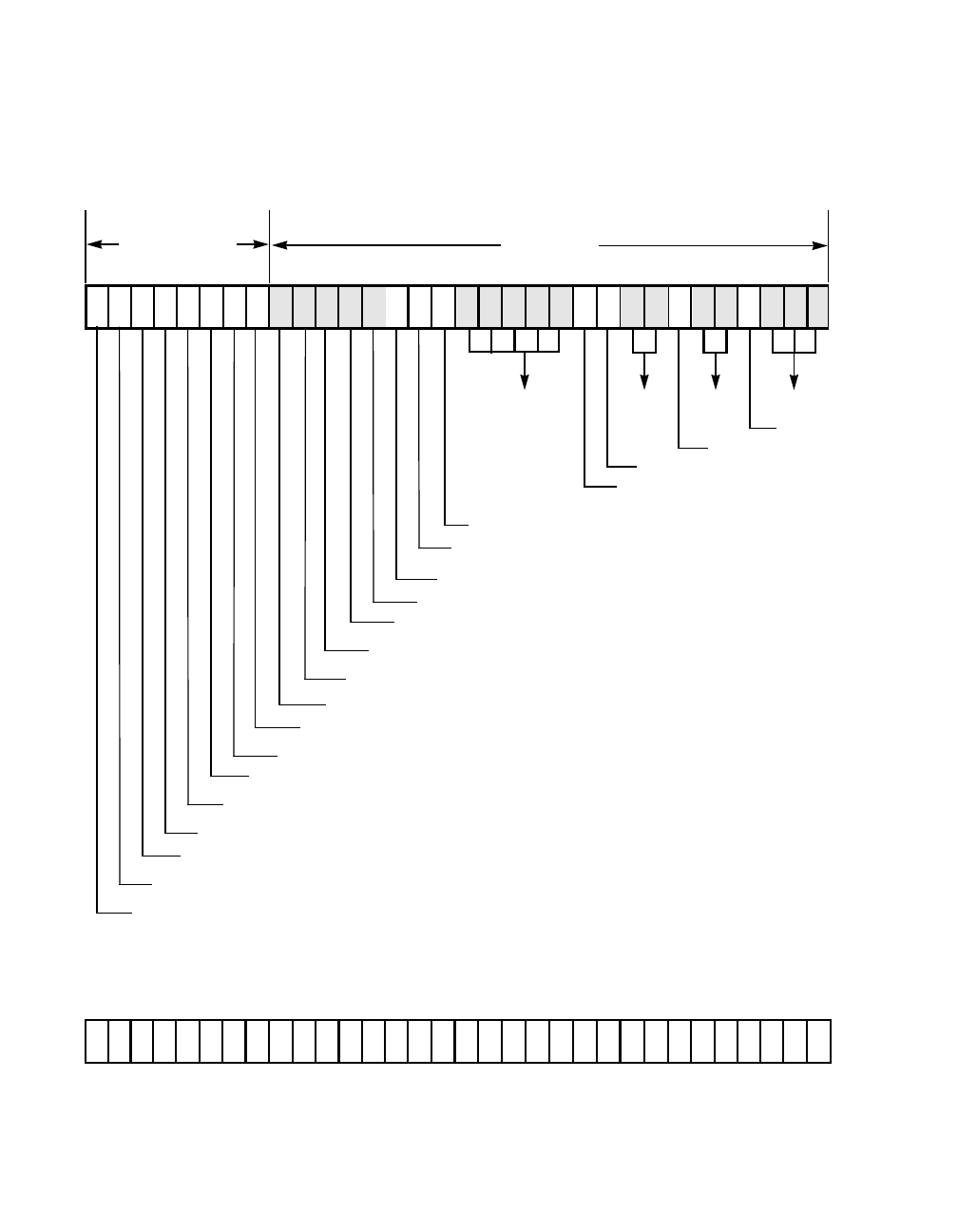

Figure 6.3 illustrates the register bit values that represent an I/O

instruction.

Figure 6.3 I/O Instruction Register

31 30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

31 30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

DSPS Register

DCMD Register DBC Register

R

RR

R

Set/Clear ATN/

Set/Clear ACK/

Set/Clear Target Mode

Set/Clear Carry

Encoded Destination ID 0

Encoded Destination ID 1

Encoded Destination ID 2

Reserved

Reserved

Reserved

Reserved

Reserved

Select with ATN/

Table Indirect Mode

Relative Address Mode

Opcode Bit 0

Opcode Bit 1

Opcode Bit 2

1 - Instruction Type - I/O

0 - Instruction Type - I/O

32-bit Jump Address

Second 32-bit Word of the I/O Instruction