5-9

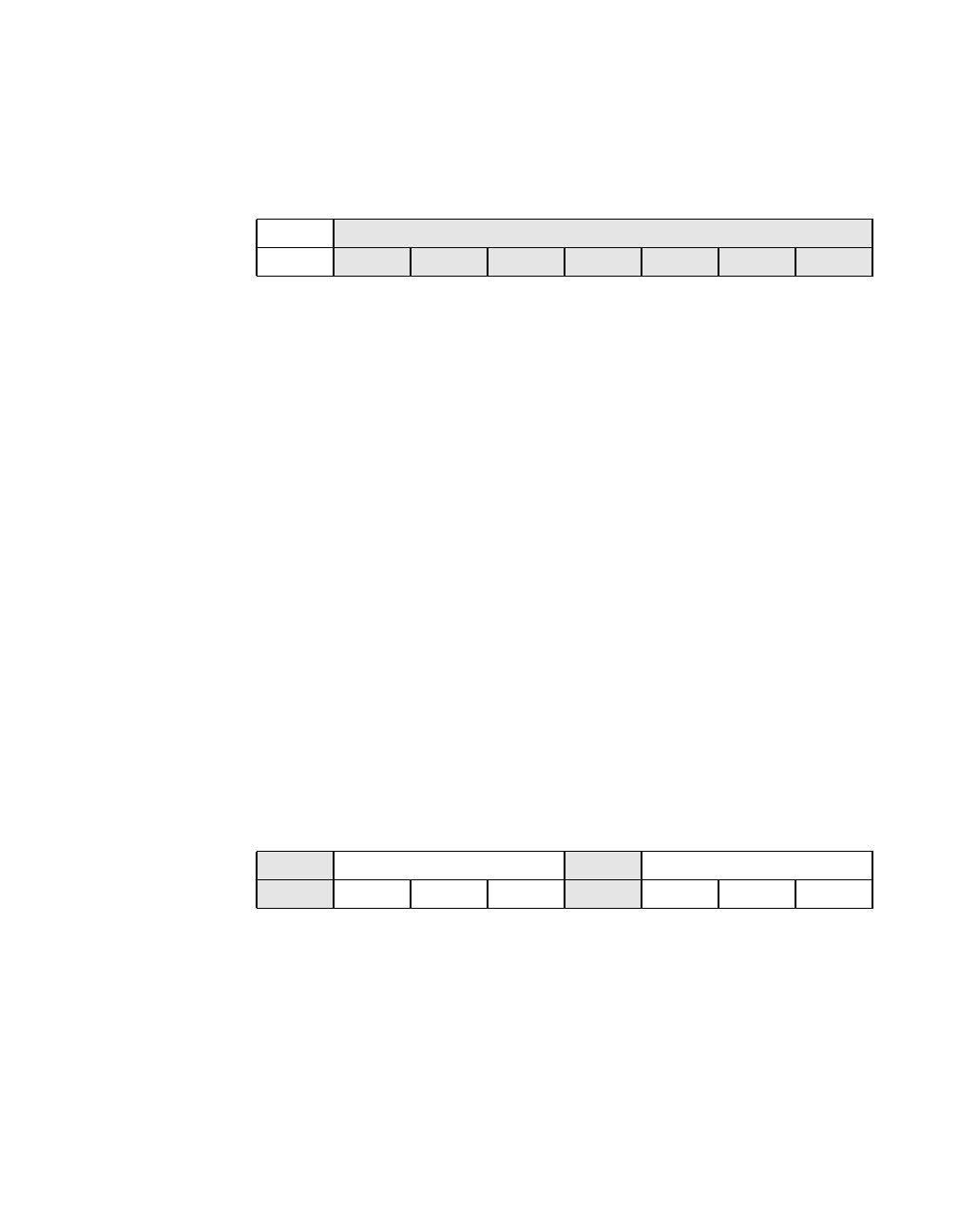

Register: 0x02 (0x82)

SCSI Control Two (SCNTL2)

Read/Write

SDU SCSI Disconnect Unexpected 7

This bit is valid in the initiator mode only. When this bit is

set, the SCSI core is not expecting the SCSI bus to enter

the Bus Free phase. If it does, an unexpected disconnect

error is generated (see the Unexpected Disconnect bit in

the SCSI Interrupt Status Zero (SIST0) register, bit 2).

During normal SCRIPTS mode operation, this bit is set

automatically whenever the SCSI core is reselected, or

successfully selects another SCSI device. The SDU bit

should be cleared with a register write (move 0x07 and

SCNTL2 to SCNTL2) before the SCSI core expects a

disconnect to occur, normally prior to sending an Abort,

Abort Tag, Bus Device Reset, Clear Queue or Release

Recovery message, or before deasserting SACK/ after

receiving a Disconnect command or Command Complete

message.

R Reserved [6:0]

Register: 0x03 (0x83)

SCSI Control Three (SCNTL3)

Read/Write

R Reserved 7

SCF[2:0] Synchronous Clock Conversion Factor [6:4]

These bits select the factor by which the frequency of

SCLK is divided before being presented to the

synchronous SCSI control logic. The bit encoding is

displayed in Table 5.1. For synchronous receive, the

output of this divider is always divided by 4 and that value

76 0

SDU R

0 x x x x x x x

76 432 0

R SCF[2:0] R CCF[2:0]

0000x000