5-3

ARB[1:0] Arbitration Mode Bits 1 and 0 [7:6]

Simple Arbitration

1. The LSI53C810A waits for a bus free condition to

occur.

2. It asserts SBSY/ and its SCSI ID (contained in the

SCSI Chip ID (SCID) register) onto the SCSI bus. If

the SSEL/ signal is asserted by another SCSI

device, the LSI53C810A deasserts SBSY/,

deasserts its ID, and sets the Lost Arbitration bit

(bit 3) in the SCSI Status Zero (SSTAT0) register.

3. After an arbitration delay, the CPU should read the

SCSI Bus Data Lines (SBDL) register to check if a

higher priority SCSI ID is present. If no higher

priority ID bit is set, and the Lost Arbitration bit is not

set, the LSI53C810A wins arbitration.

4. Once the LSI53C810A wins arbitration, SSEL/ must

be asserted using the SCSI Output Control Latch

(SOCL) for a bus clear plus a bus settle delay

(1.2 µs) before a low level selection is performed.

Full Arbitration, Selection/Reselection

1. The LSI53C810A waits for a bus free condition.

2. It asserts SBSY/ and its SCSI ID (the highest priority

ID stored in the SCSI Chip ID (SCID) register) onto

the SCSI bus.

3. If the SSEL/ signal is asserted by another SCSI

device or if the LSI53C810A detects a higher priority

ID, the LSI53C810A deasserts BSY, deasserts its ID,

and waits until the next bus free state to try

arbitration again.

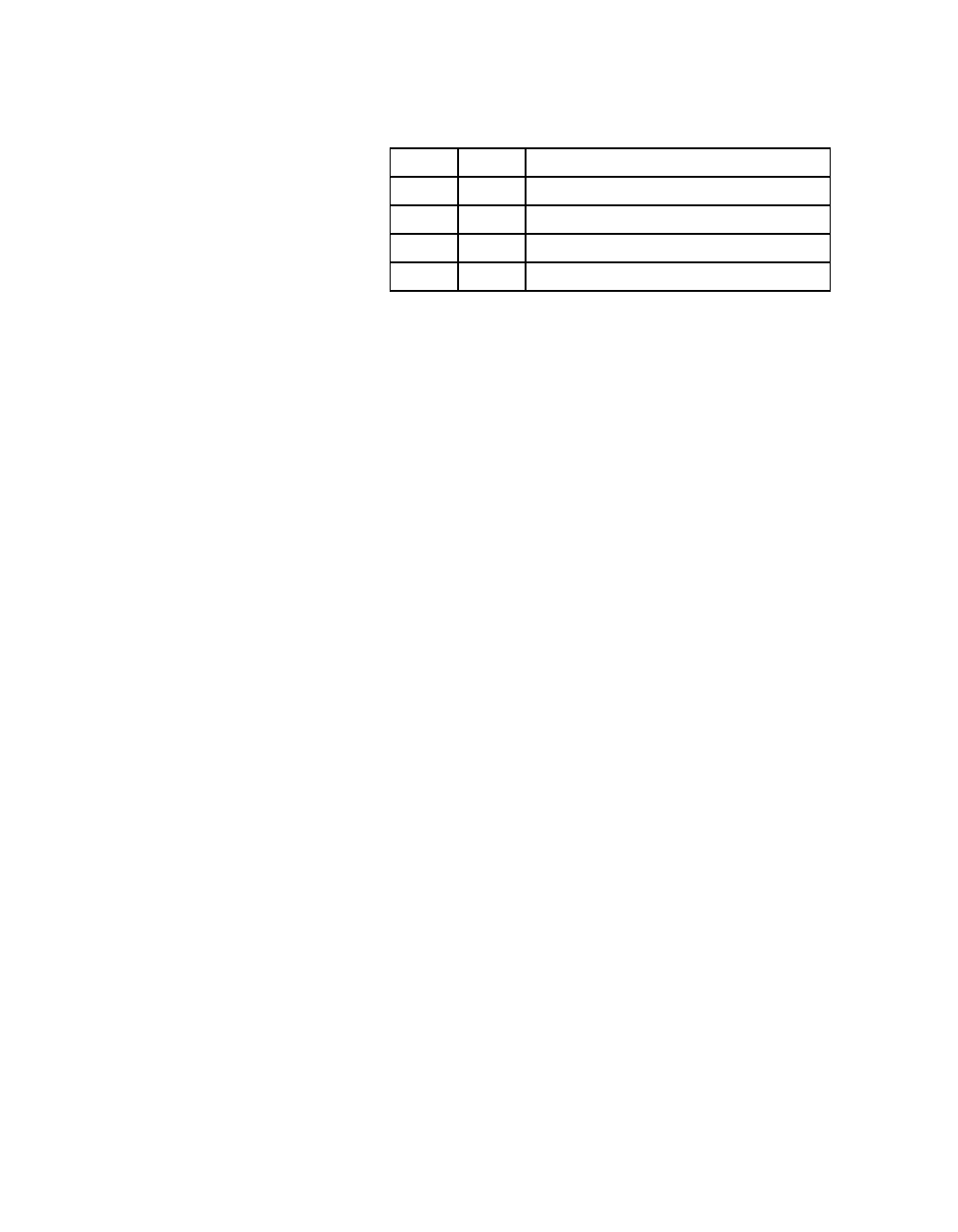

ARB1 ARB0 Arbitration Mode

0 0 Simple arbitration

0 1 Reserved

1 0 Reserved

1 1 Full arbitration, selection/reselection