Memory Move Instructions 6-37

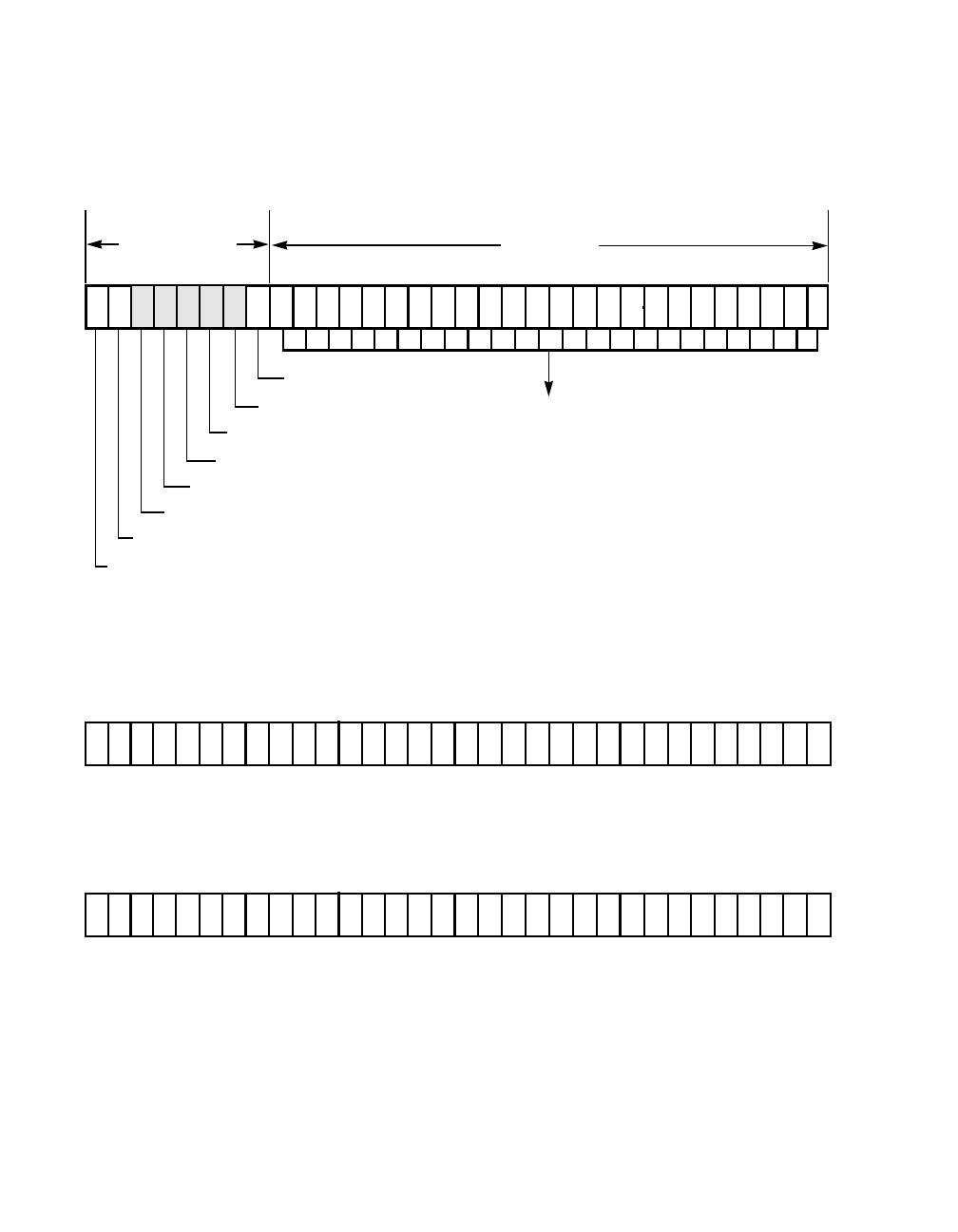

Figure 6.6 illustrates the register bit values that represent a Memory

Move instruction.

Figure 6.6 Memory to Memory Move Instruction

31 30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

31 30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

DSPS Register

DCMD Register DBC Register

24-bit Memory Move Byte Counter

No Flush

0 (Reserved)

0 (Reserved)

0 (Reserved)

0 (Reserved)

0 (Reserved)

1 - Instruction Type - Memory Move

1 - Instruction Type - Memory Move

31 30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

TEMP Register