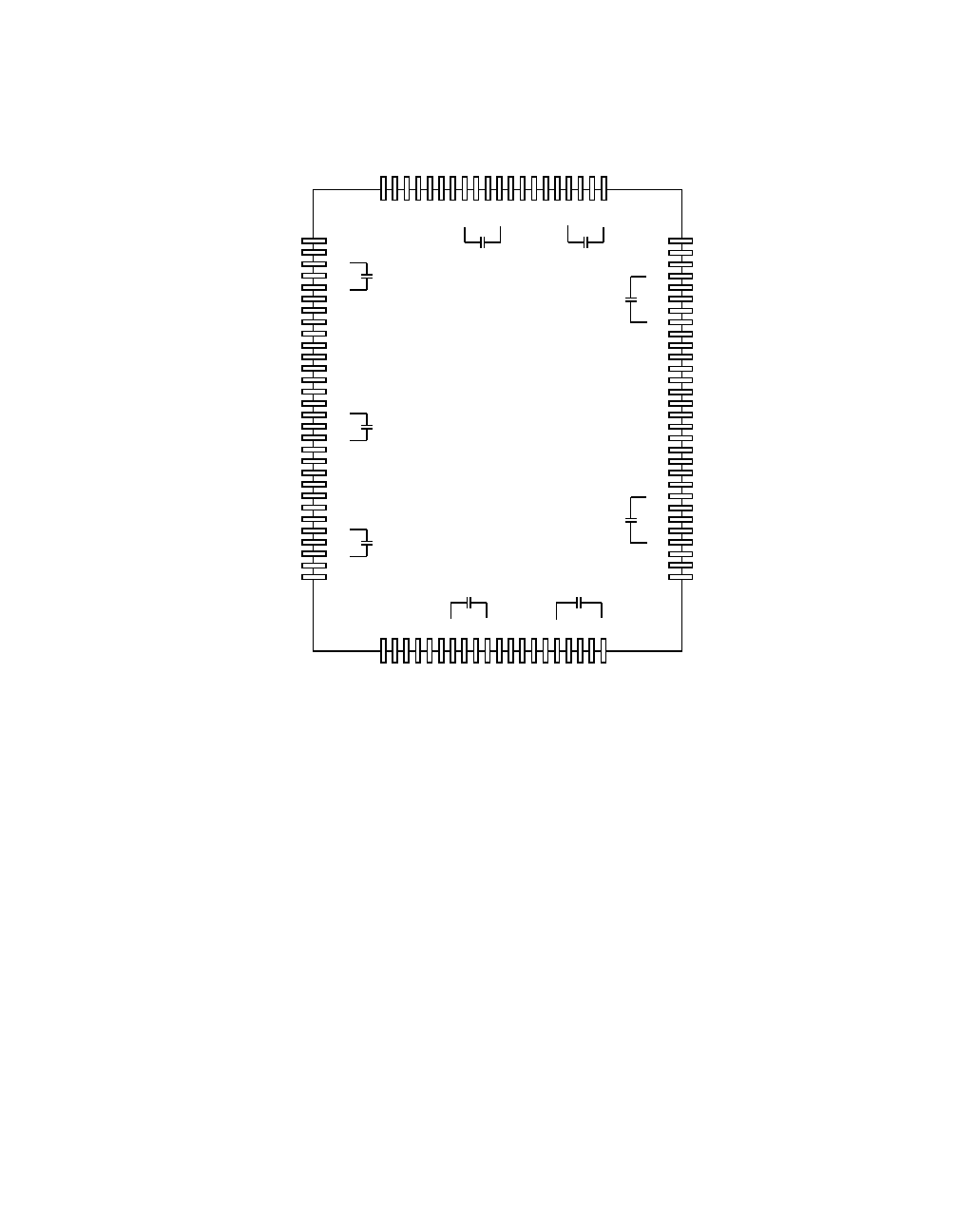

4-2 Signal Descriptions

Figure 4.1 LSI53C810A Pin Diagram

A slash (/) at the end of the signal name indicates that the active state

occurs when the signal is at a LOW voltage. When the slash is absent,

the signal is active at a HIGH voltage.

AD21

V

DD

-I

V

SS

-I

AD16

FRAME/

DEVSEL/

STOP/

V

SS

-I

V

SS

-I

AD13

AD12

V

DD

-I

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

IRDY/

TRDY/

Quad Flat Pack

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

AD20

AD19

AD17

C_BE2/

V

SS

-I

V

DD

-I

C_BE1/

AD15

V

SS

-I

AD10

AD18

V

SS

-I

PERR/

PA R

AD14

AD11

CLK

SERR/

SD0/

V

SS

-S

SD5/

SDP/

SBSY/

V

SS

-S

SSEL/

SREQ/

V

DD

-S

MAC/_TESTOUT

80

78

76

74

72

70

68

66

64

62

60

58

56

54

SD6/

SD7/

79

77

75

73

71

69

67

65

63

61

59

57

55

53

RST/

V

DD

-S

SD2/

SD4/

V

SS

-S

SATN/

SMSG/

V

SS

-S

SIO/

SD1/

SD3/

SACK/

SRST/

SCD/

V

SS

-I

C_BE0/

V

SS-

I

V

DD-

I

AD1

V

DD

-C

IRQ/

AD3

V

SS

-I

AD9

AD8

AD6

AD4

AD2

AD0

V

SS

-C

AD7

AD5

GPIO0_FETCH/

GPIO1_MASTER/ GNT

AD31

AD30

VSS-I

AD28

V

DD

-I

AD27

AD25

81

83

85

87

V

SS

-C

AD26

V

SS

-I

C_BE3/

IDSEL

AD22

V

SS

-I

89

91

93

95

97

99

V

DD

-C

REQ/

AD29

AD24

AD23

32

34

36

38

40

42

44

46

48

50

31

33

35

37

39

41

43

45

47

49

LSI53C810A

100-pin

TESTIN

SCLK

52

51

82

84

86

88

90

92

94

96

98

100