PCI Bus Interface Signals 4-7

4.1.3 Interface Control Signals

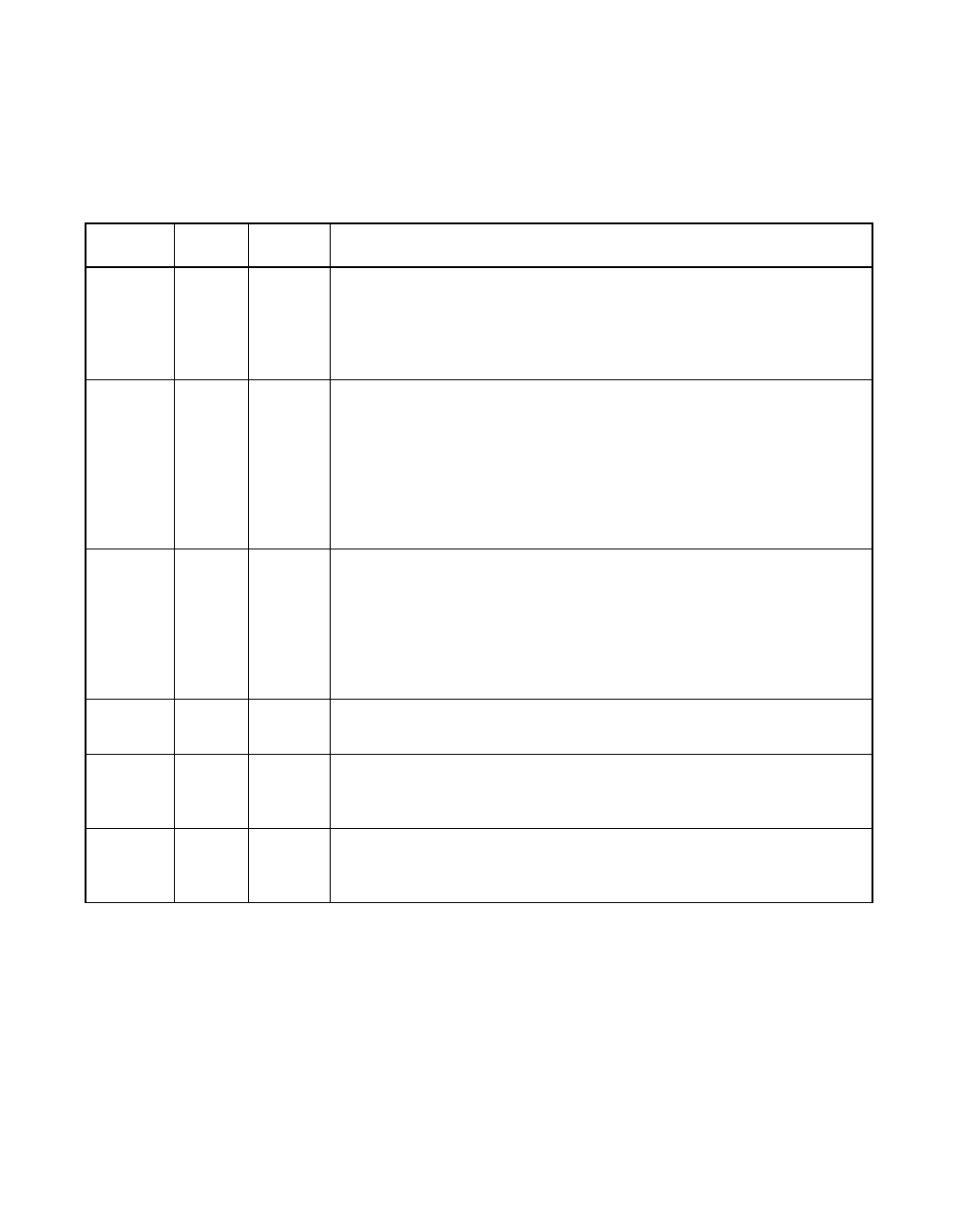

Table 4.4 describes the Interface Control Signals group.

Table 4.4 Interface Control Signals

Name Pin No. Type Description

FRAME/ 11 S/T/S Cycle Frame is driven by the current master to indicate the beginning

and duration of an access. FRAME/ is asserted to indicate that a bus

transaction is beginning. While FRAME/ is asserted, data transfers

continue. While FRAME/ is deasserted, either the transaction is in the

final data phase or the bus is idle.

TRDY/ 14 S/T/S Target Ready indicates the target agent’s (selected device’s) ability

to complete the current data phase of the transaction. TRDY/ is used

with IRDY/. A data phase is completed on any clock when used with

IRDY/. A data phase is completed on any clock when both TRDY/ and

IRDY/ are sampled asserted. During a read, TRDY/ indicates that

valid data is present on AD[31:0]. During a write, it indicates that the

target is prepared to accept data. Wait cycles are inserted until both

IRDY/ and TRDY/ are asserted together.

IRDY/ 12 S/T/S Initiator Ready indicates the initiating agent’s (bus master’s) ability to

complete the current data phase of the transaction. IRDY/ is used

with TRDY/. A data phase is completed on any clock when both IRDY/

and TRDY/ are sampled asserted. During a write, IRDY/ indicates that

valid data is present on AD[31:0]. During a read, it indicates that the

master is prepared to accept data. Wait cycles are inserted until both

IRDY/ and TRDY/ are asserted together.

STOP/ 17 S/T/S Stop indicates that the selected target is requesting the master to

stop the current transaction.

DEVSEL/ 15 S/T/S Device Select indicates that the driving device has decoded its

address as the target of the current access. As an input, it indicates

to a master whether any device on the bus has been selected.

IDSEL 97 I Initialization Device Select is used as a chip select in place of the

upper 24 address lines during configuration read and write

transactions.