5-12 Operating Registers

R Reserved [4:3]

ENC[2:0] Encoded LSI53C810A Chip SCSI ID [2:0]

These bits are used to store the LSI53C810A encoded

SCSI ID. This is the ID which the chip asserts when

arbitrating for the SCSI bus. The IDs that the

LSI53C810A responds to when being selected or

reselected are configured in the Response ID (RESPID)

register. The priority of the 8 possible IDs, in descending

order is:

Register: 0x05 (0x85)

SCSI Transfer (SXFER)

Read/Write

When using Table Indirect I/O commands, bits [7:0] of this register are

loaded from the I/O data structure.

Note: For additional information on how the synchronous transfer

rate is determined, refer to Chapter 2, “Functional Descrip-

tion.”

TP[2:0] SCSI Synchronous Transfer Period [7:5]

These bits determine the SCSI synchronous transfer

period (XFERP) used by the LSI53C810A when sending

synchronous SCSI data in either the initiator or target

mode. These bits control the programmable dividers in

the chip.

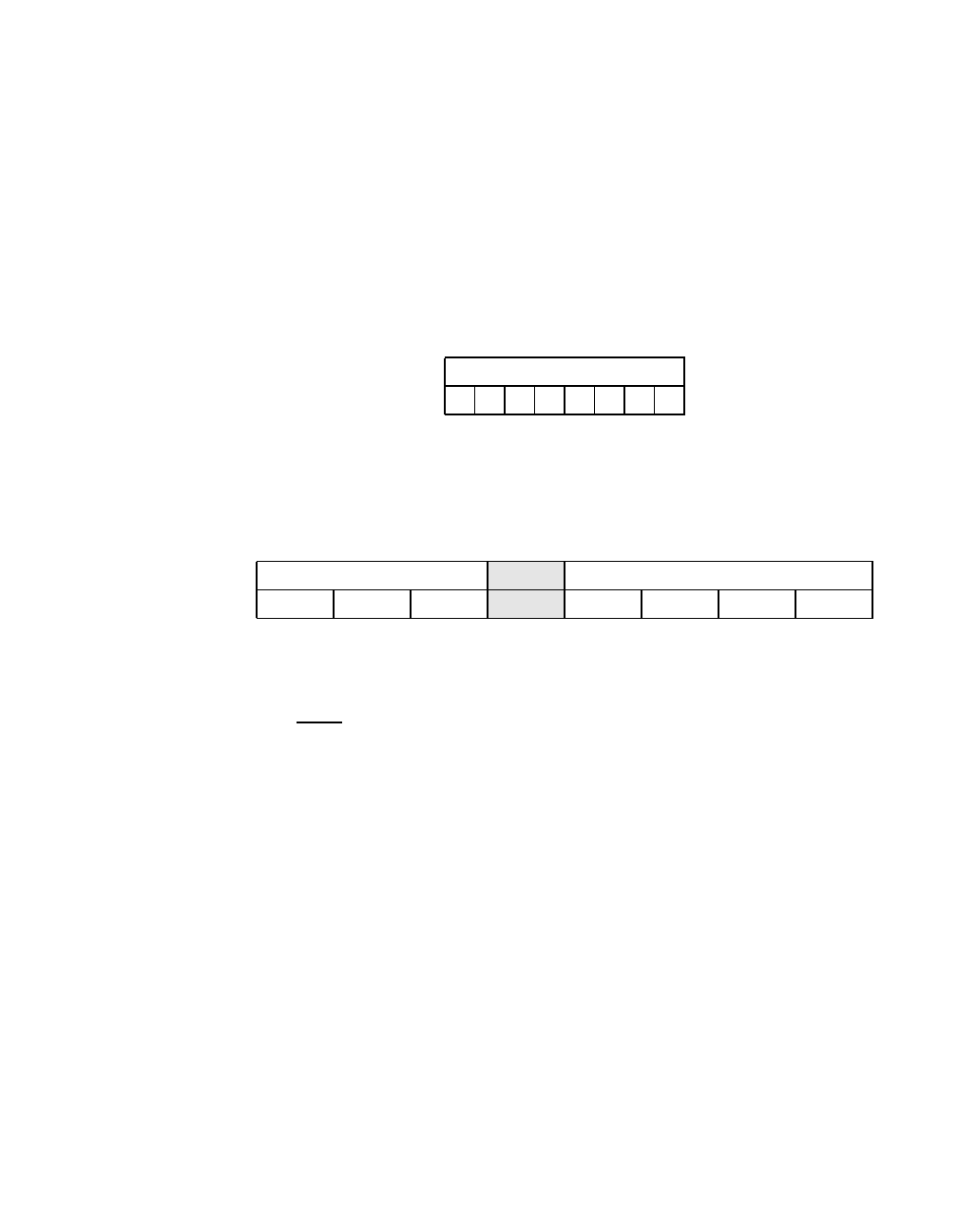

Highest Lowest

76543210

7 543 0

TP[2:0] R MO[3:0]

000x0000