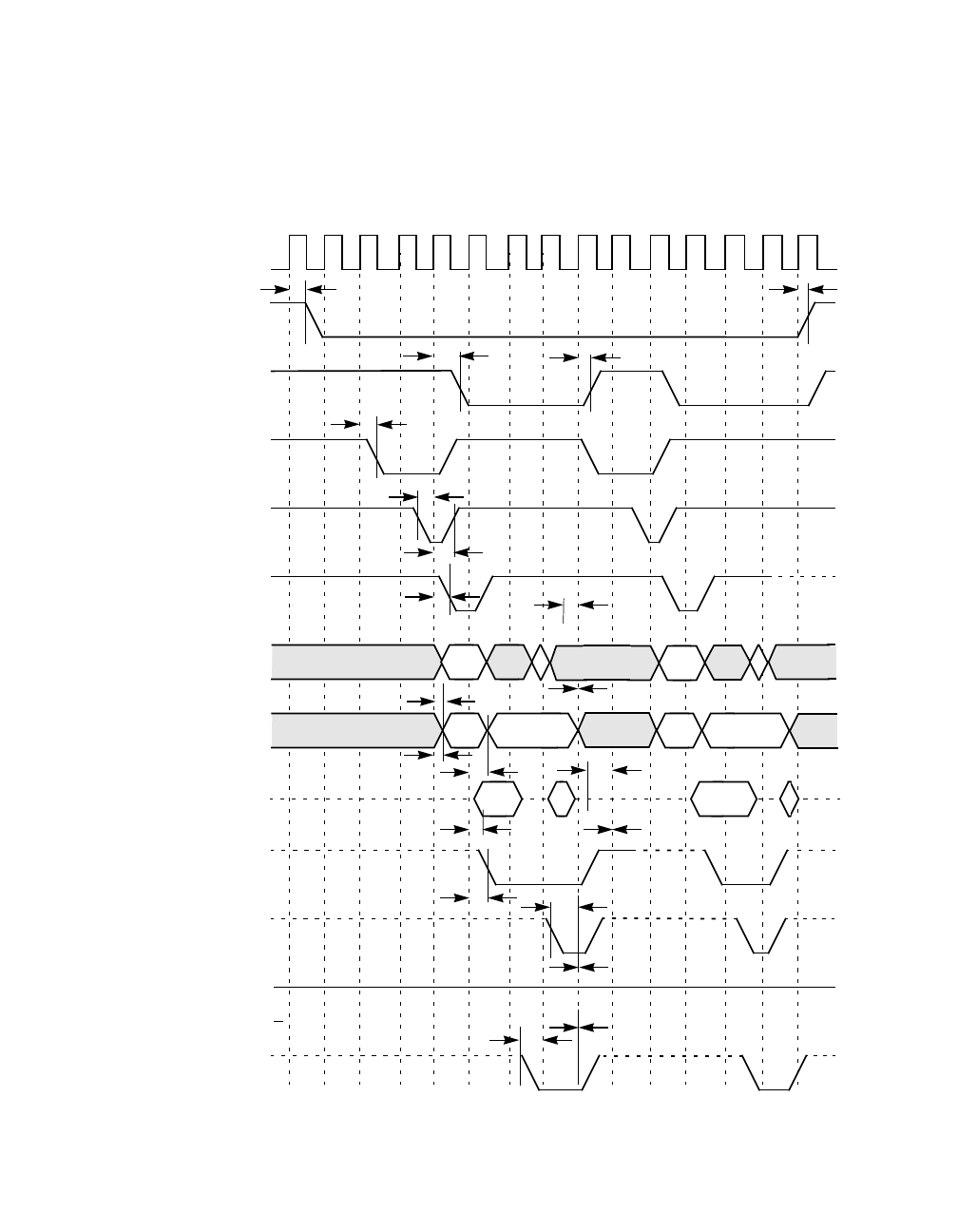

PCI Interface Timing Diagrams 7-17

7.4.2 Initiator Timing

Figure 7.13 through Figure 7.18 describe initiator timing.

Figure 7.13 OpCode Fetch, Nonburst

CLK

(Driven by System)

FRAME/

(Driven by LSI53C810A)

AD/

(Driven by LSI53C810A-

C_BE/

(Driven by LSI53C810A)

PAR/

(Driven by LSI53C810A-

IRDY/

(Driven by LSI53C810A)

TRDY/

(Driven by Target)

STOP/

(Driven by Target)

DEVSEL/

(Driven by Target)

Addr/ Target-Data)

Addr; Target-Data)

GNT/

(Driven by Arbiter)

REQ/

(Driven by LSI53C810A)

GPIO1_MASTER/

(Driven by LSI53C810A)

GPIO0_FETCH/

(Driven by LSI53C810A)

Addr

Out

Addr

Out

CMD

BE

BE

CMD

t

1

t

2

t

3

t

10

t

8

t

7

t

9

t

4

t

6

t

5

t

1

t

1

t

1

t

2

t

2

t

2

t

3

t

3

t

3

t

3

t

3

Data

In

Data

In