5-6 Operating Registers

Register: 0x01 (0x81)

SCSI Control One (SCNTL1)

Read/Write

EXC Extra Clock Cycle of Data Setup 7

When this bit is set, an extra clock period of data setup

is added to each SCSI data transfer. The extra data setup

time can provide additional system design margin, though

it affects the SCSI transfer rates. Clearing this bit disables

the extra clock cycle of data setup time. Setting this bit

only affects SCSI send operations.

ADB Assert SCSI Data Bus 6

When this bit is set, the LSI53C810A drives the contents

of the SCSI Output Data Latch (SODL) register onto the

SCSI data bus. When the LSI53C810A is an initiator, the

SCSI I/O signal must be inactive to assert the SCSI Out-

put Data Latch (SODL) contents onto the SCSI bus.

When the LSI53C810A is a target, the SCSI I/O signal

must be active to assert the SCSI Output Data Latch

(SODL) contents onto the SCSI bus. The contents of the

SCSI Output Data Latch (SODL) register can be asserted

at any time, even before the LSI53C810A is connected to

the SCSI bus. Clear this bit when executing SCSI

SCRIPTS. It is normally used only for diagnostics testing

or operation in low level mode.

DHP Disable Halt on Parity Error or ATN (Target Only) 5

The DHP bit is only defined for target mode. When this

bit is cleared, the LSI53C810A halts the SCSI data

transfer when a parity error is detected or when the

SATN/ signal is asserted. If SATN/ or a parity error is

received in the middle of a data transfer, the LSI53C810A

may transfer up to three additional bytes before halting to

synchronize between internal core cells. During

synchronous operation, the LSI53C810A transfers data

until there are no outstanding synchronous offsets. If the

LSI53C810A is receiving data, any data residing in the

DMA FIFO is sent to memory before halting.

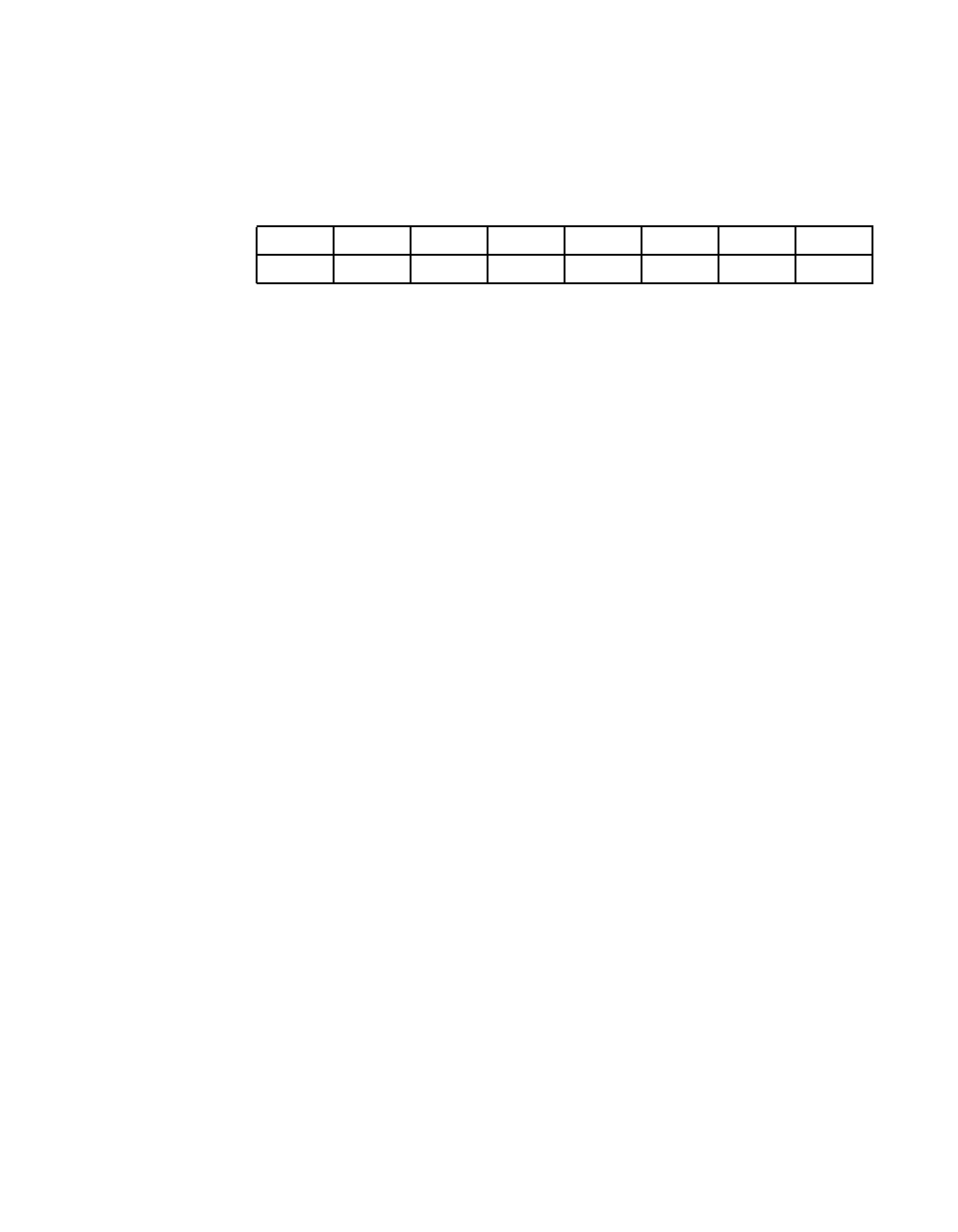

76543210

EXC ADB DHP CON RST AESP IARB SST

00000000