SCSI Bus Interface Signals 4-9

4.2 SCSI Bus Interface Signals

The SCSI signal definitions are organized into the following functional

groups: SCSI Bus Interface Signals and Additional Interface Signals.

4.2.1 SCSI Bus Interface Signals

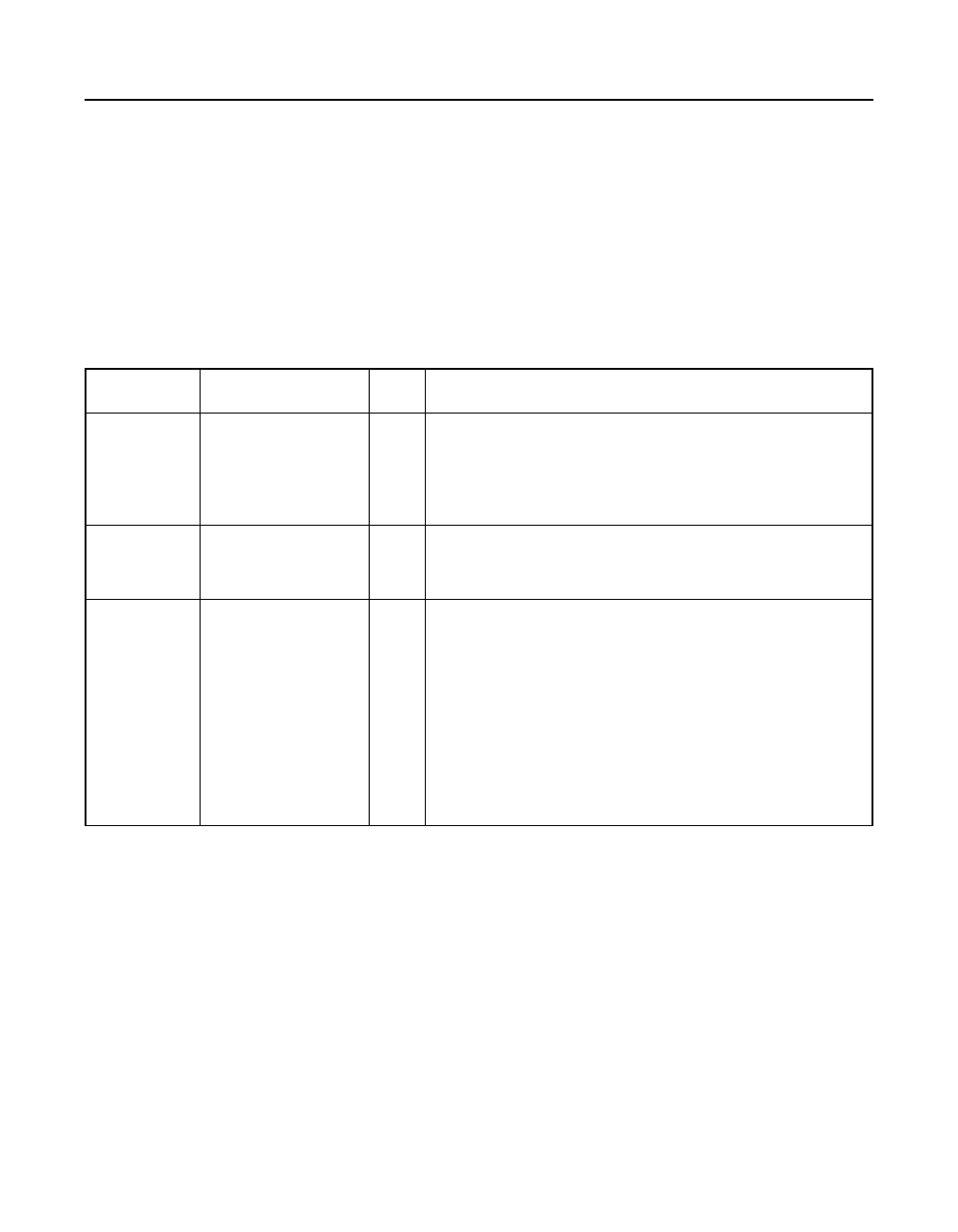

Table 4.7 describes the SCSI Bus Interface Signals group.

Table 4.7 SCSI Bus Interface Signals

Name Pin No. Type Description

SCLK 51 I SCSI Clock is used to derive all SCSI-related timings.

The speed of this clock is determined by the application

requirements. In some applications, SCLK may be

sourced internally from the PCI bus clock (CLK). If SCLK

is internally sourced, tie the SCLK pin LOW.

SD[7:0],

SDP

67, 69, 70, 71, 72,

74, 75, 76, 66

I/O SCSI Data includes the following data lines and parity

signals: SD[7:0] (8-bit SCSI data bus), and SDP (SCSI

data parity bit).

SCTRL/ 57, 55, 60, 56, 62,

64, 65, 61, 59

I/O SCSI Control includes the following signals:

SCD/ SCSI phase line, command/data

SIO/ SCSI phase line, input/output

SMSG/ SCSI phase line, message

SREQ/ Data handshake signal from target device

SACK/ Data handshake signal from initiator device

SBSY/ SCSI bus arbitration signal, busy

SATN/ SCSI Attention, the initiator is requesting a

message out phase

SRST/ SCSI bus reset

SSEL/ SCSI bus arbitration signal, select device