2-10 Functional Description

Step 2. Read bit 7 in the SCSI Status Zero (SSTAT0) register to

determine if any bytes are left in the SCSI Input Data Latch

(SIDL) register. If bit 7 is set in SSTAT0, then the SCSI Input

Data Latch (SIDL) register is full.

Synchronous SCSI Receive –

Step 1. Subtract the seven least significant bits of the DMA Byte

Counter (DBC) register from the 7-bit value of the DMA FIFO

(DFIFO) register. AND the result with 0x7F for a byte count

between zero and 80.

Step 2. Read the SCSI Status One (SSTAT1) register and examine bits

[7:4], the binary representation of the number of valid bytes in

the SCSI FIFO, to determine if any bytes are left in the SCSI

FIFO.

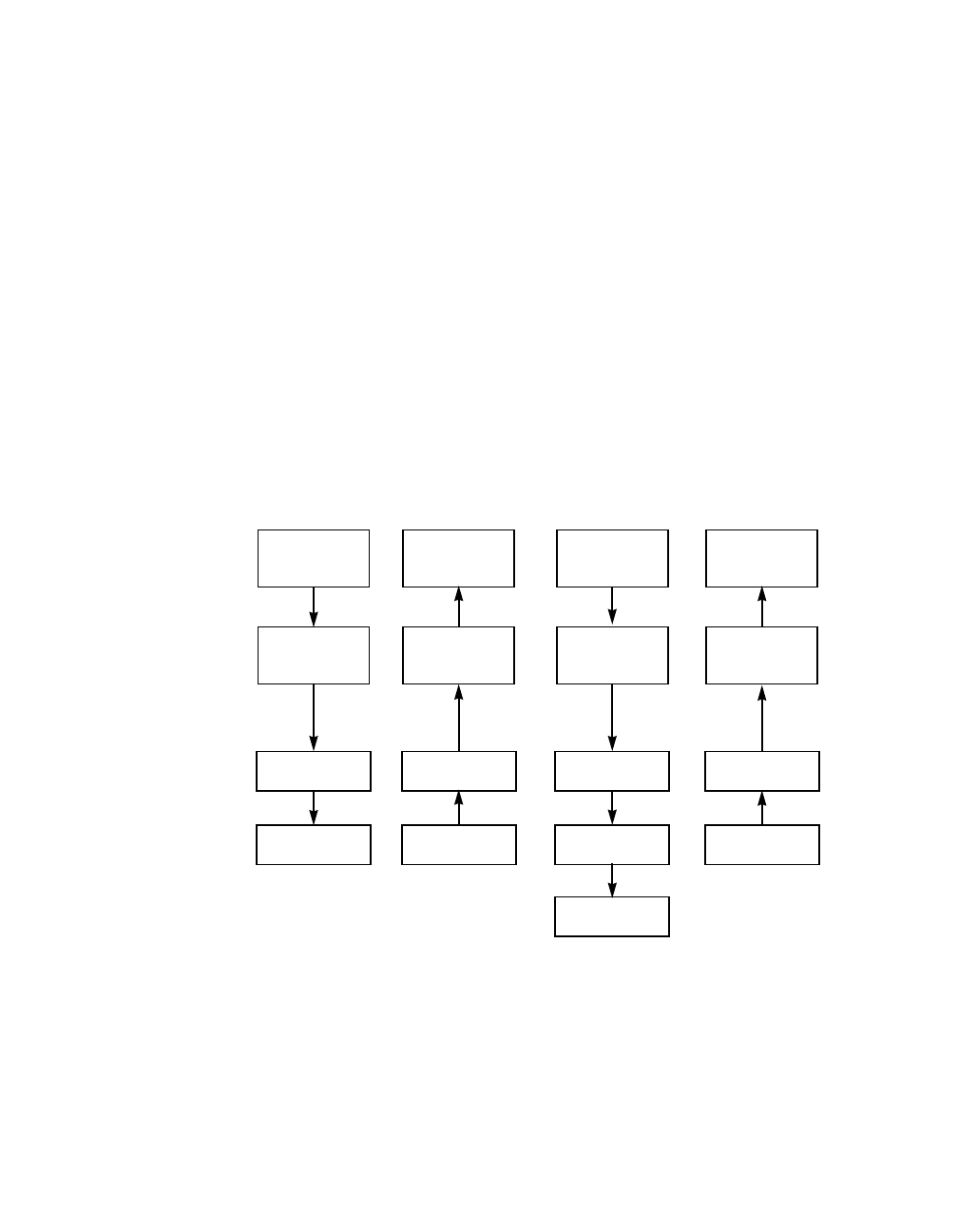

Figure 2.2 LSI53C810A Host Interface Data Paths

PCI

DMA FIFO

(4-bytes x 20)

DMA FIFO

(4-bytes x 20)

SODL Register SIDL Register

SCSI InterfaceSCSI Interface

Asynchronous

SCSI Send

Asynchronous

SCSI Receive

DMA FIFO

(4-bytes x 20)

DMA FIFO

(4-bytes x 20)

SODR Register

SODL Register

SCSI Interface

SCSI Interface

SCSI FIFO

Synchronous

SCSI Send

Synchronous

SCSI Receive

Interface

PCI

Interface

PCI

Interface

PCI

Interface