3-39

BUS INTERFACE UNIT

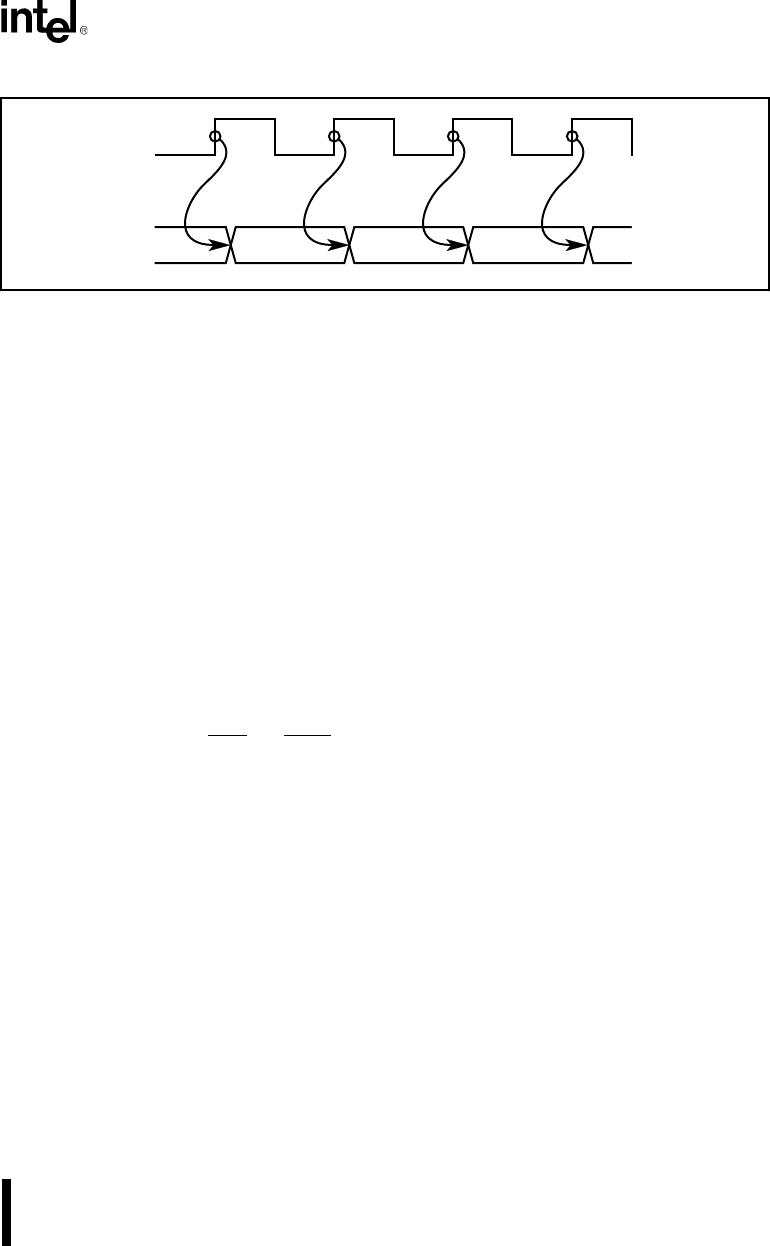

Figure 3-33. Queue Status Timing

3.7 MULTI-MASTER BUS SYSTEM DESIGNS

The BIU supports protocols for transferring control of the local bus between itself and other de-

vices capable of acting as bus masters. To support such a protocol, the BIU uses a hold request

input (HOLD) and a hold acknowledge output (HLDA) as bus transfer handshake signals. To

gain control of the bus, a device asserts the HOLD input, then waits until the HLDA output goes

active before driving the bus. After HLDA goes active, the requesting device can take control of

the local bus and remains in control of the bus until HOLD is removed.

3.7.1 Entering Bus HOLD

In responding to the hold request input, the BIU floats the entire address and data bus, and many

of the control signals. Figure 3-34 illustrates the timing sequence when acknowledging the hold

request. Table 3-8 lists the states of the BIU pins when HLDA is asserted. All device pins not

mentioned in Table 3-8 or shown in Figure 3-34 remain either active (e.g., CLKOUT and

T1OUT) or inactive (e.g., UCS

and INTA). Refer to the data sheet for specific details of pin func-

tions during a bus hold.

QS0, QS1

CLKOUT

A1059-0A