INTERRUPT CONTROL UNIT

8-28

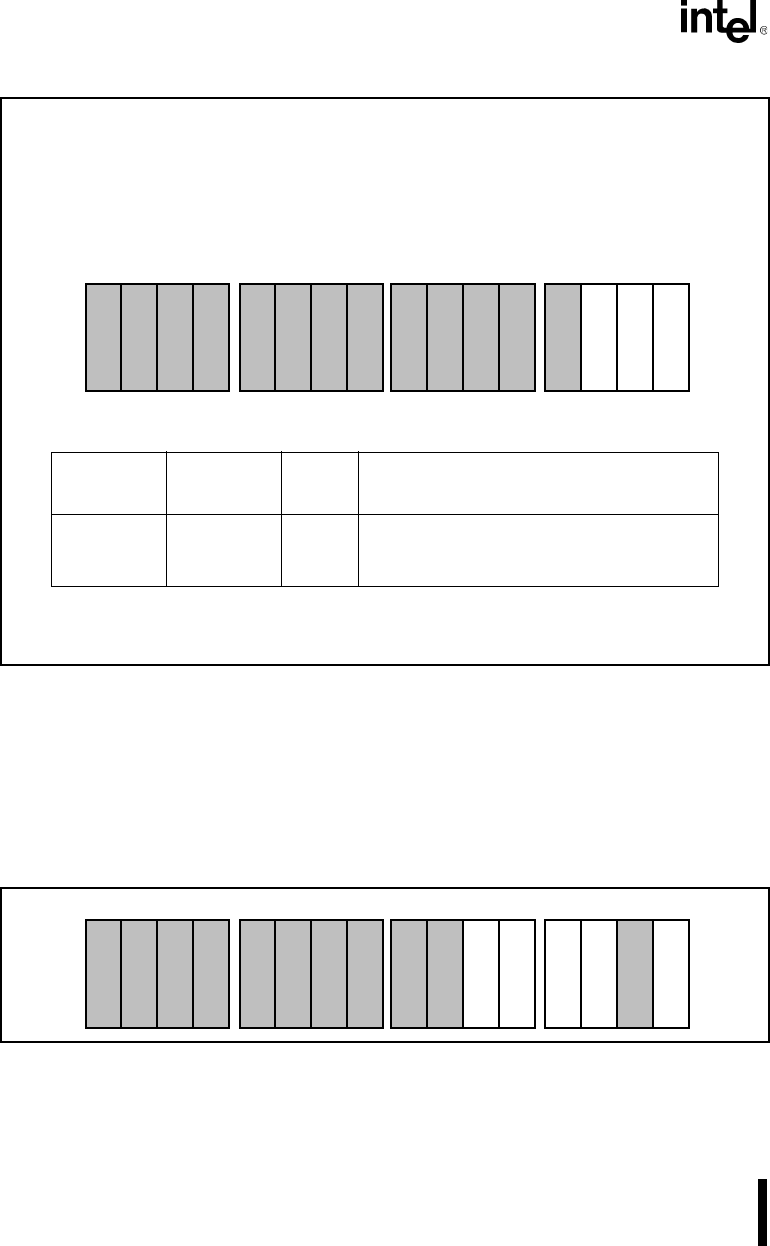

Figure 8-18. End-of-Interrupt Register in Slave Mode

8.5.1.3 Other Registers

The Priority Mask register is identical in Slave mode and Master mode. The Interrupt Request,

Interrupt Mask, and In-Service registers retain the same function, but individual bits differ to ac-

commodate the addition of the individual timer interrupts and the deletion of the external inter-

rupts. Figure 8-19 shows the bit positions for Slave mode.

Figure 8-19. Request, Mask, and In-Service Registers

Register Name: End-of-Interrupt Register (in Slave Mode)

Register Mnemonic: EOI

Register Function: Used to issue the EOI command

Bit

Mnemonic

Bit Name

Reset

State

Function

VT2:0 Interrupt

Type

0 Write the three LSBs of the interrupt type (see

Table 8-5) to these bits to issue an EOI

command in slave mode.

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1197-A0

15 0

V

T

0

V

T

2

V

T

1

15 0

T

M

R

0

D

M

A

0

D

M

A

1

T

M

R

2

T

M

R

1