BUS INTERFACE UNIT

3-44

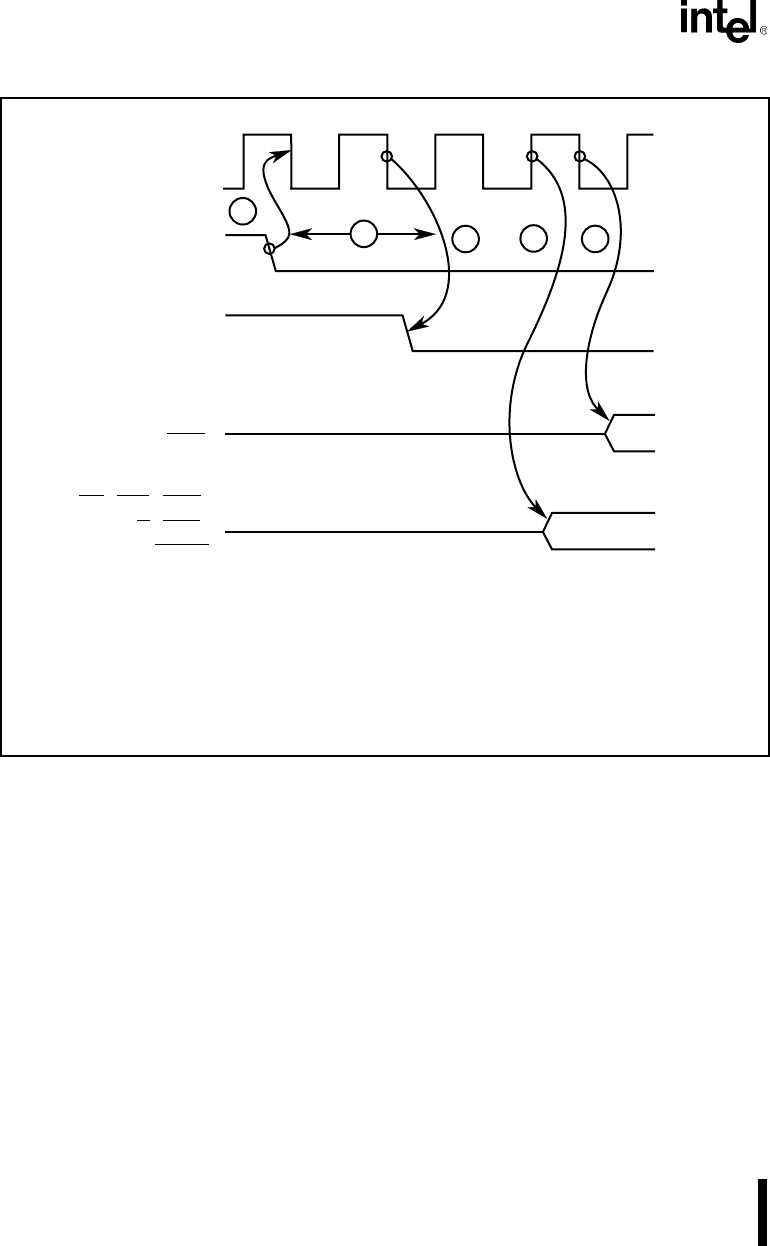

Figure 3-37. Exiting HOLD

3.8 BUS CYCLE PRIORITIES

The BIU arbitrates requests for bus cycles from the Execution Unit, the integrated peripherals

(e.g., Interrupt Control Unit) and external bus masters (i.e., bus hold requests). The list below

summarizes the priorities for all bus cycle requests (from highest to lowest).

1. Instruction execution read/write following a non-pipelined effective address calculation.

2. Refresh bus cycles.

3. Bus hold request.

4. Single step interrupt vectoring sequence.

5. Non-Maskable interrupt vectoring sequence.

HLDA

CLKOUT

HOLD

1

4

3

AD15:0

DEN

RD, WR, BHE,

DT/R, S2:0,

A19:16, LOCK

5

2

NOTES:

1. T

HVCL

: HOLD recognition setup to clock low

2. : HOLD internally synchronized

3. T

CLHAV

: Clock low to HLDA low

4. T

CHCV

: Clock high to signal active (high or low)

5. T

CLAV

: Clock low to signal active (high or low)

A1063-0A